请教大家一个问题。

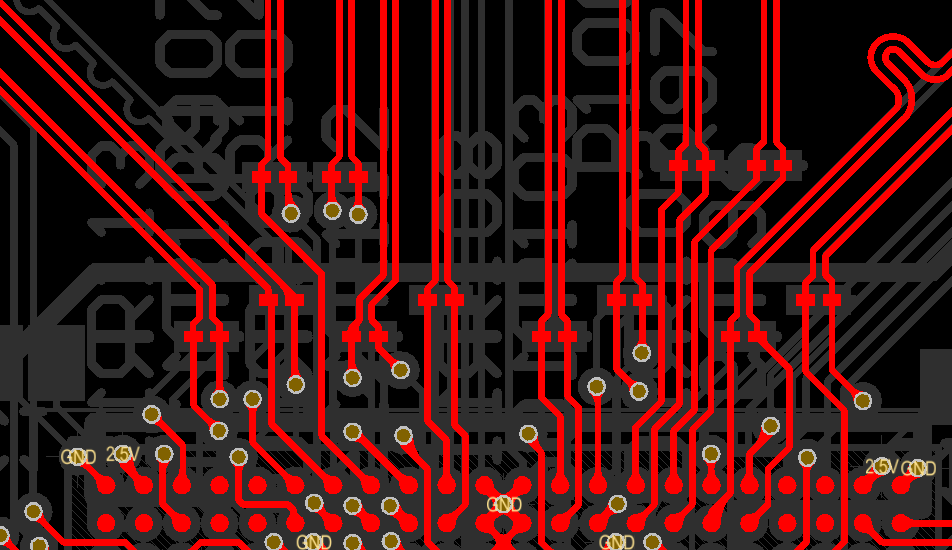

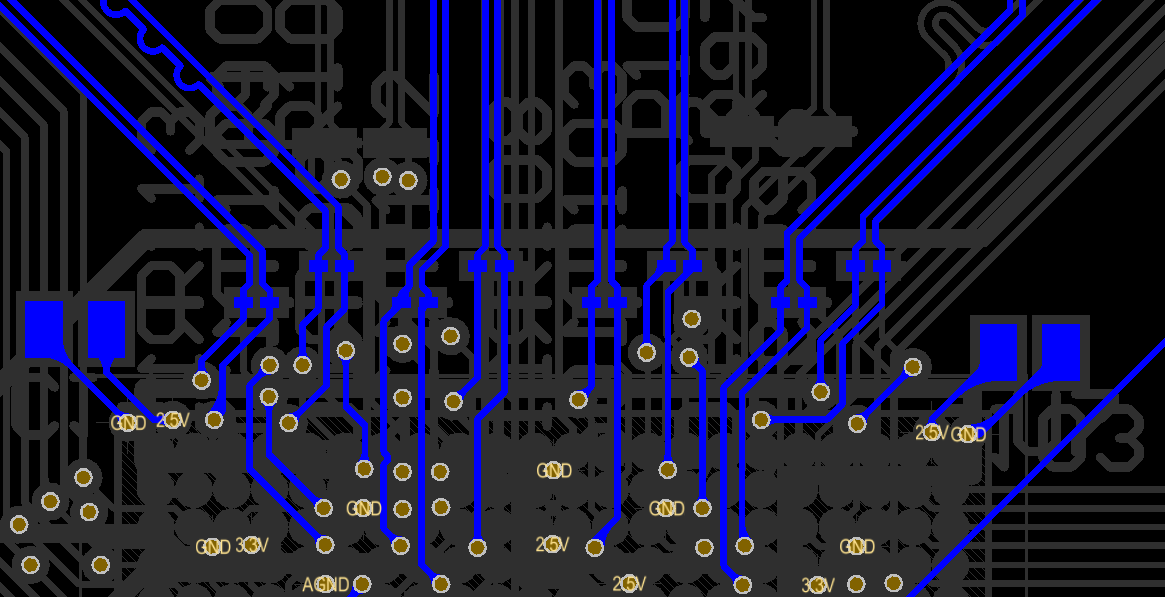

芯片采用的差分线传输数字数据,芯片输出一共有10对LVDS差分走线,两对时钟,8对数据线。

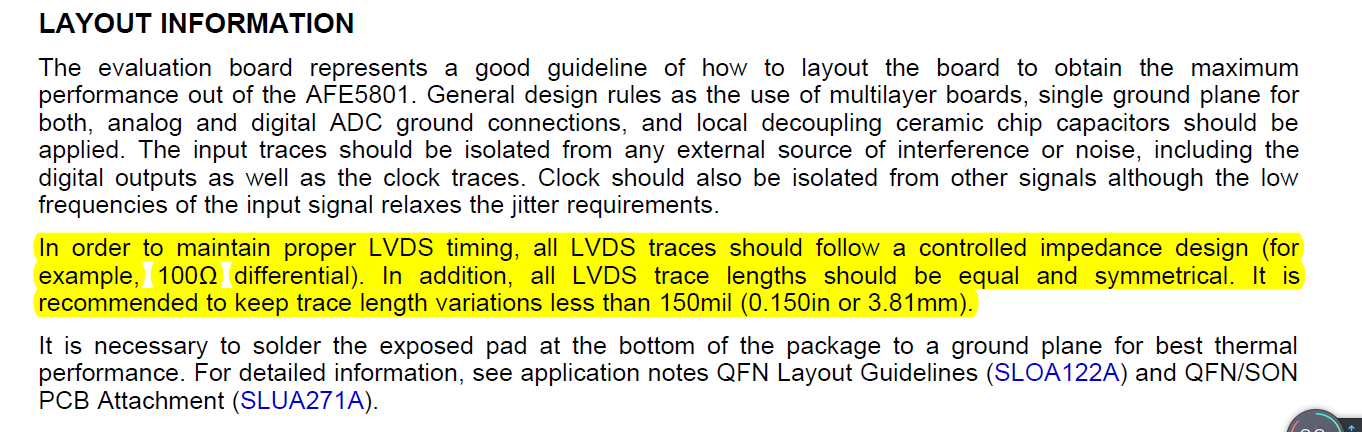

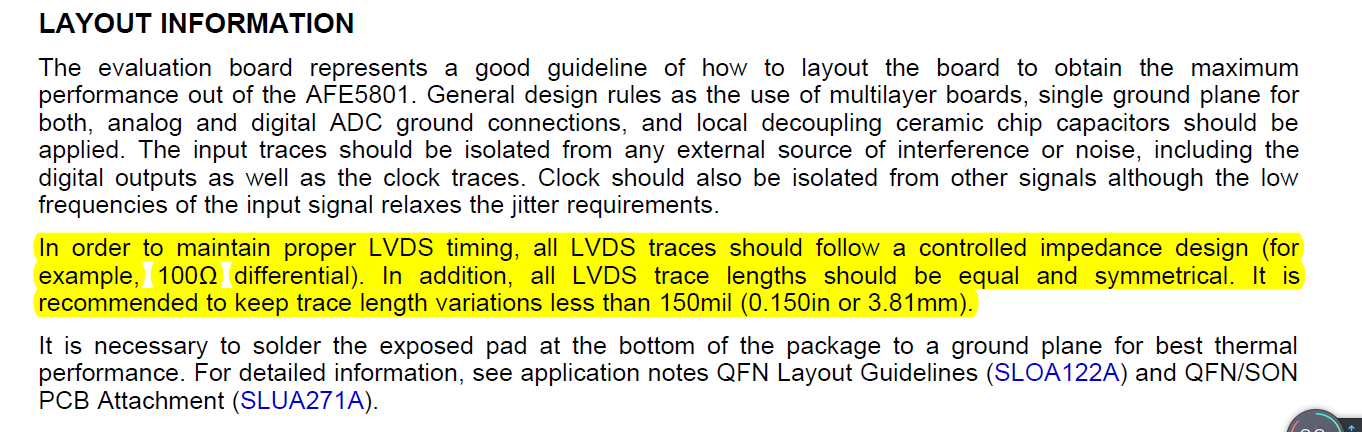

截图是芯片手册中提到的内容。

问题1:它是说明每一对之间相差长度吗?我举例解释一下:比如说AD1_P AD1_N 与 AD2_P AD2_N 这两对之间的差距小于150mil? 还是还是一对差分线中的P线和N线的相差长度小于150mil?

问题2:我在PCB布线上遇到了难题,不知道要保证每对等长需要的长度差限制范围。频率是120MHz。

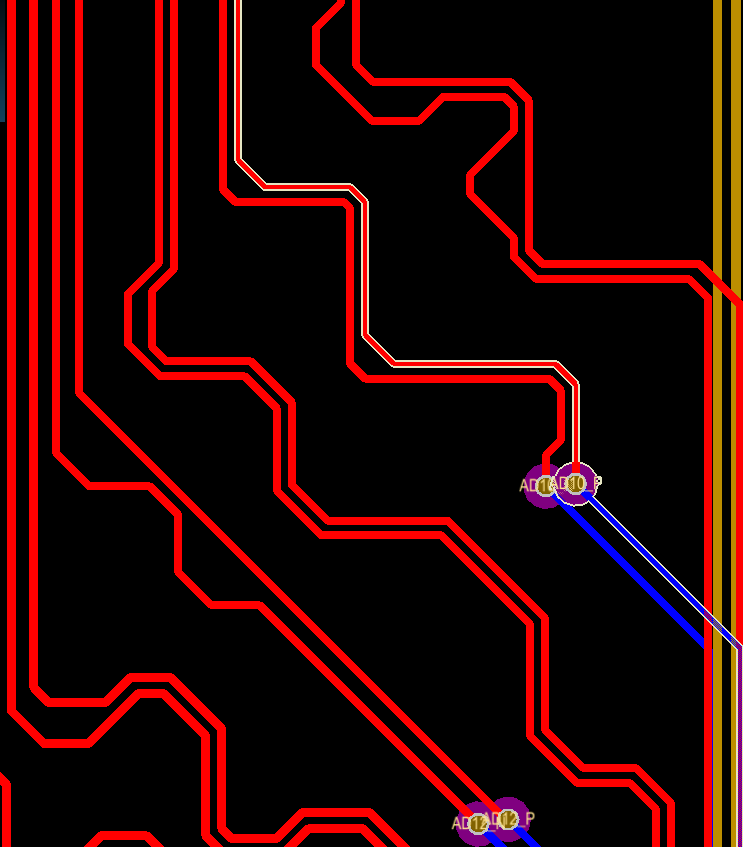

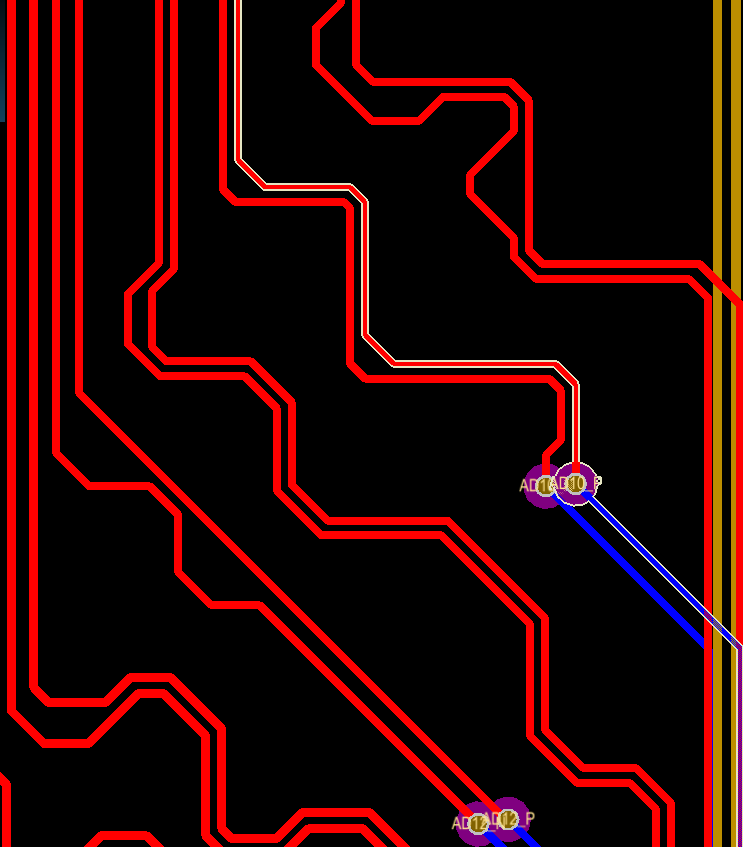

而且每对差分线保持等长应该也有长度差的容量吧,不然我无法保持两根线平行了,比如下图。

希望大神解答!非常感谢!

发帖

发帖 与我相关

与我相关 我的任务

我的任务 分享

分享