2,432

社区成员

发帖

发帖 与我相关

与我相关 我的任务

我的任务 分享

分享

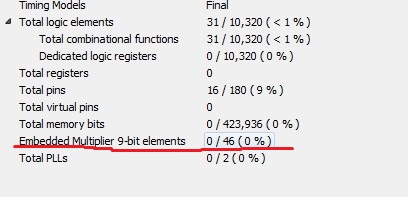

module mult(outcome,a,b); input [7:0] a,b; output [15:0]outcome;

assign outcome = a*b; endmodulemodule mult(outcome,a,b); input [7:0] a,b; output [15:0]outcome;

assign outcome = a*b; endmodule