在网络上找了许久,研究了下IIC上拉电阻计算。发现网络上总是有个文章被转来转去,我仔细看了下总觉的有错:

就是这篇文章:http://blog.sina.com.cn/s/blog_5f103c9c0100ly0r.html

被转来转去的额····

看下里面的第一个公式:应该是 Vdd(max) 才可以吧??

然后第二个公式里的:1us 是 1 00KHZ ? 这个是说周期么?要是周期100K不是10us ??当然那个400K的也是错的了。

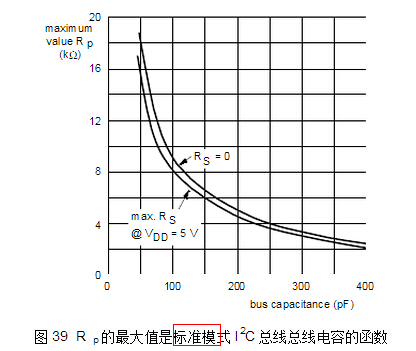

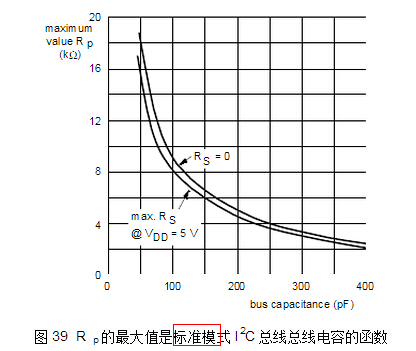

我从周工的IIC里面看到一个图是这样的,那么3.3V的时候呢?

发帖

发帖 与我相关

与我相关 我的任务

我的任务 分享

分享

好吧,我重来没有关注过这个东西!

好吧,我重来没有关注过这个东西!