CPU是如何来判断本次取指需要取多少字节的指令数据

下面是我的猜想,求拍砖指导:

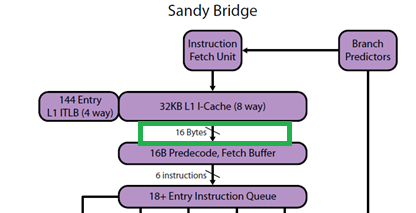

首先,CPU在取指阶段并不知道具体取多长字节的指令,所以根据指令的最大长度~15字节。CPU在一次取指阶段,直接从内存中预取15字节的指令数据。然后对该15字节的指令数据进行长度识别。

不知道上述猜测是否正确?

另外,谁知道指令寄存器(IR)的位数?

求指导,或者说说你们的理解,以及依据

发帖

发帖 与我相关

与我相关 我的任务

我的任务 分享

分享

感觉你懂的很多啊,各种编程知识都精通,学习了[/quote]

感觉你懂的很多啊,各种编程知识都精通,学习了[/quote]

感觉你懂的很多啊,各种编程知识都精通,学习了

感觉你懂的很多啊,各种编程知识都精通,学习了