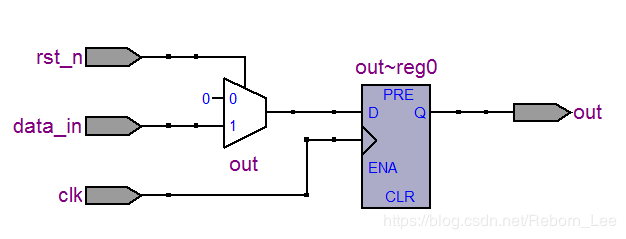

我用Verilog HDL描述的同步复位电路,为什么综合出来的电路确是异步复位的呢?

代码为:

module syn_reset(

input rst_n,

input clk,

input data_in,

output out

);

reg out;

always@(posedge clk)

begin

if(!rst_n)

out <= 1'b0;

else

out <= data_in;

end

endmodule

综合出来的电路为:

多谢大佬能够给出合理解释?使用ISE综合出来的电路为什么和我想的不一样?

发帖

发帖 与我相关

与我相关 我的任务

我的任务 分享

分享