遇到一个题目,verilog检测32位信号下降沿,这是原题目:

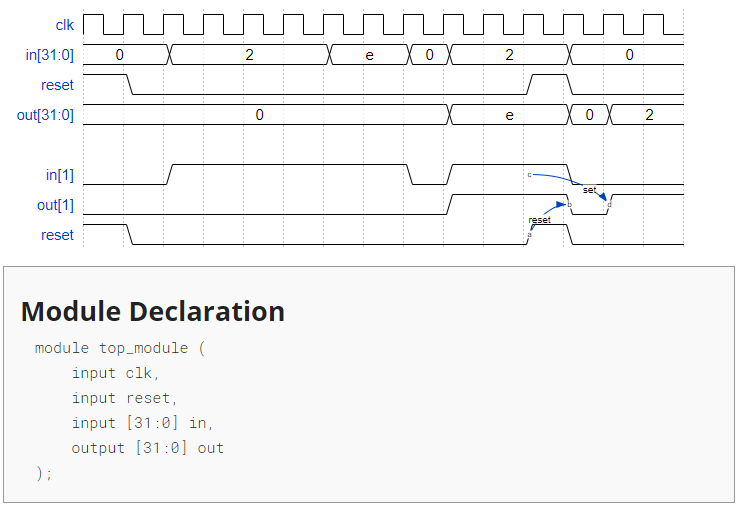

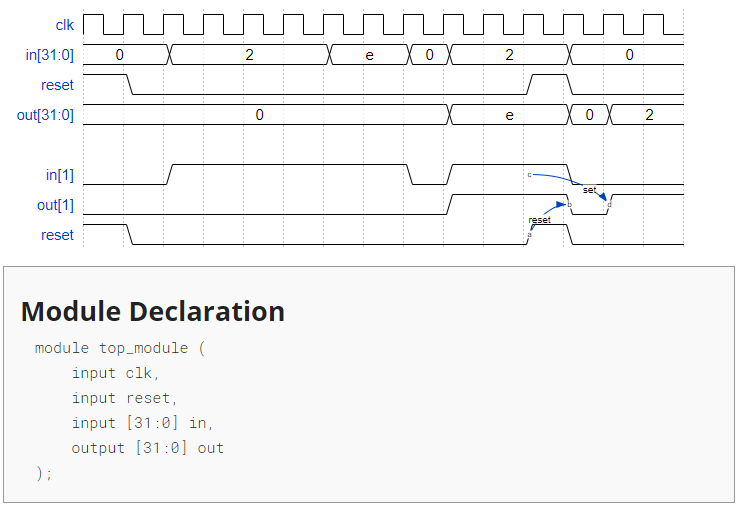

For each bit in a 32-bit vector, capture when the input signal changes from 1 in one clock cycle to 0 the next. "Capture" means that the output will remain 1 until the register is reset (synchronous reset).

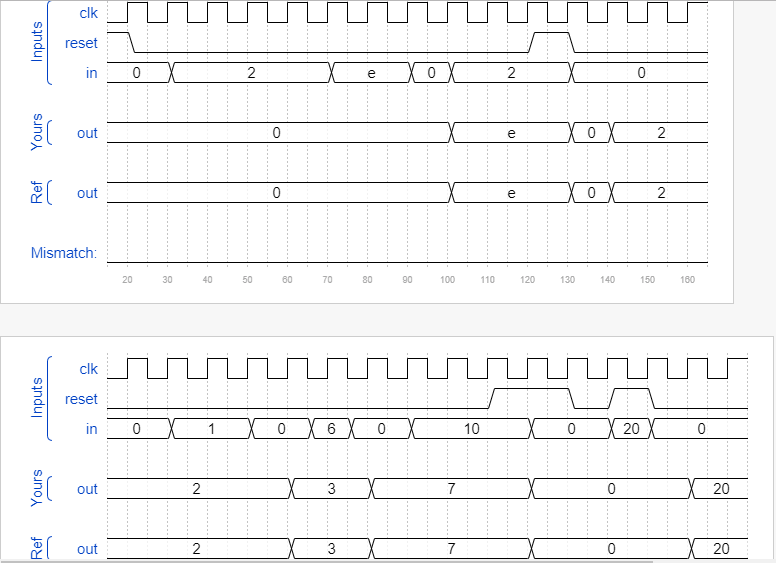

Each output bit behaves like a SR flip-flop: The output bit should be set (to 1) the cycle after a 1 to 0 transition occurs. The output bit should be reset (to 0) at the positive clock edge when reset is high. If both of the above events occur at the same time, reset has precedence. In the last 4 cycles of the example waveform below, the 'reset' event occurs one cycle earlier than the 'set' event, so there is no conflict here.

In the example waveform below, reset, in[1] and out[1] are shown again separately for clarity.

下面是我写的答案

module top_module (

input clk,

input reset,

input [31:0] in,

output reg [31:0] out

);

reg [31:0] in_reg;

always @ (posedge clk )

if(reset) out <= 32'b0 ;

else

begin

for (int i=0; i<32; ++i)

begin

if ((in_reg[i]==1)&&(in==0))

out[i] <= 1;

end

end

always @ (posedge clk )

begin

in_reg <= in;

end

endmodule

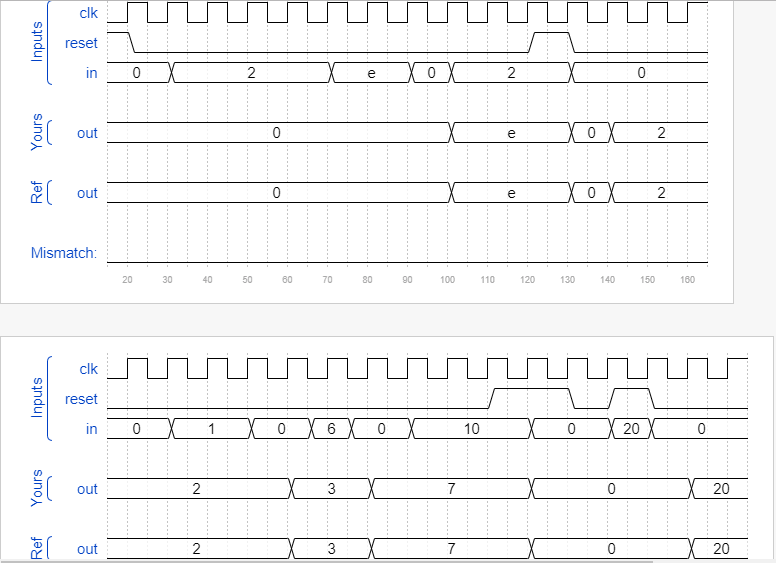

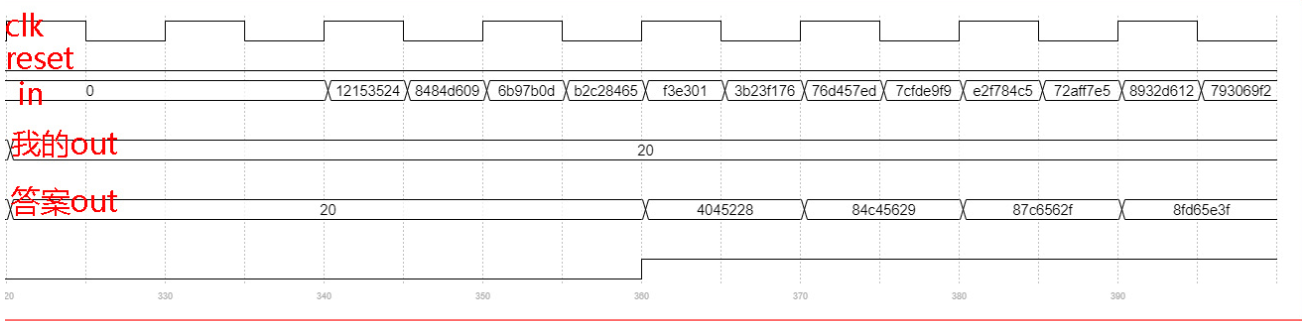

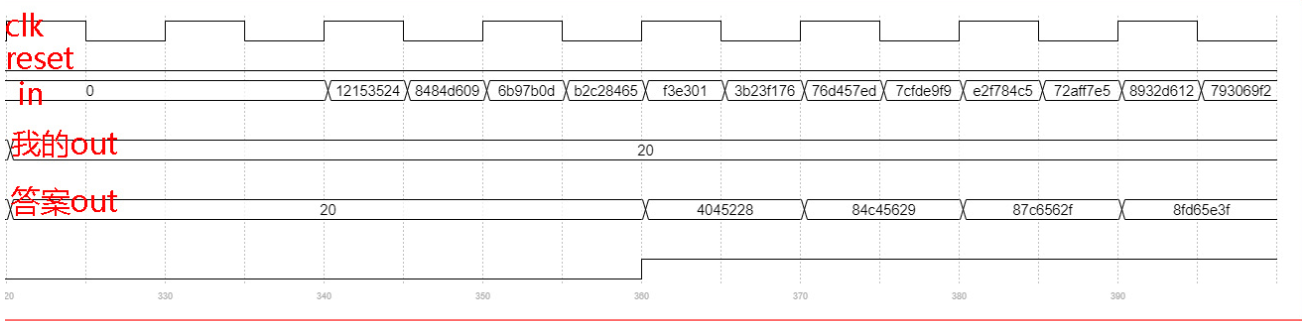

仿真结果:YOURS表示我的仿真结果,REF是标准答案仿真结果,Mismatch是匹配结果,前面都是匹配的,到第360个clk附近我的结果就不对是为什么

发帖

发帖 与我相关

与我相关 我的任务

我的任务 分享

分享