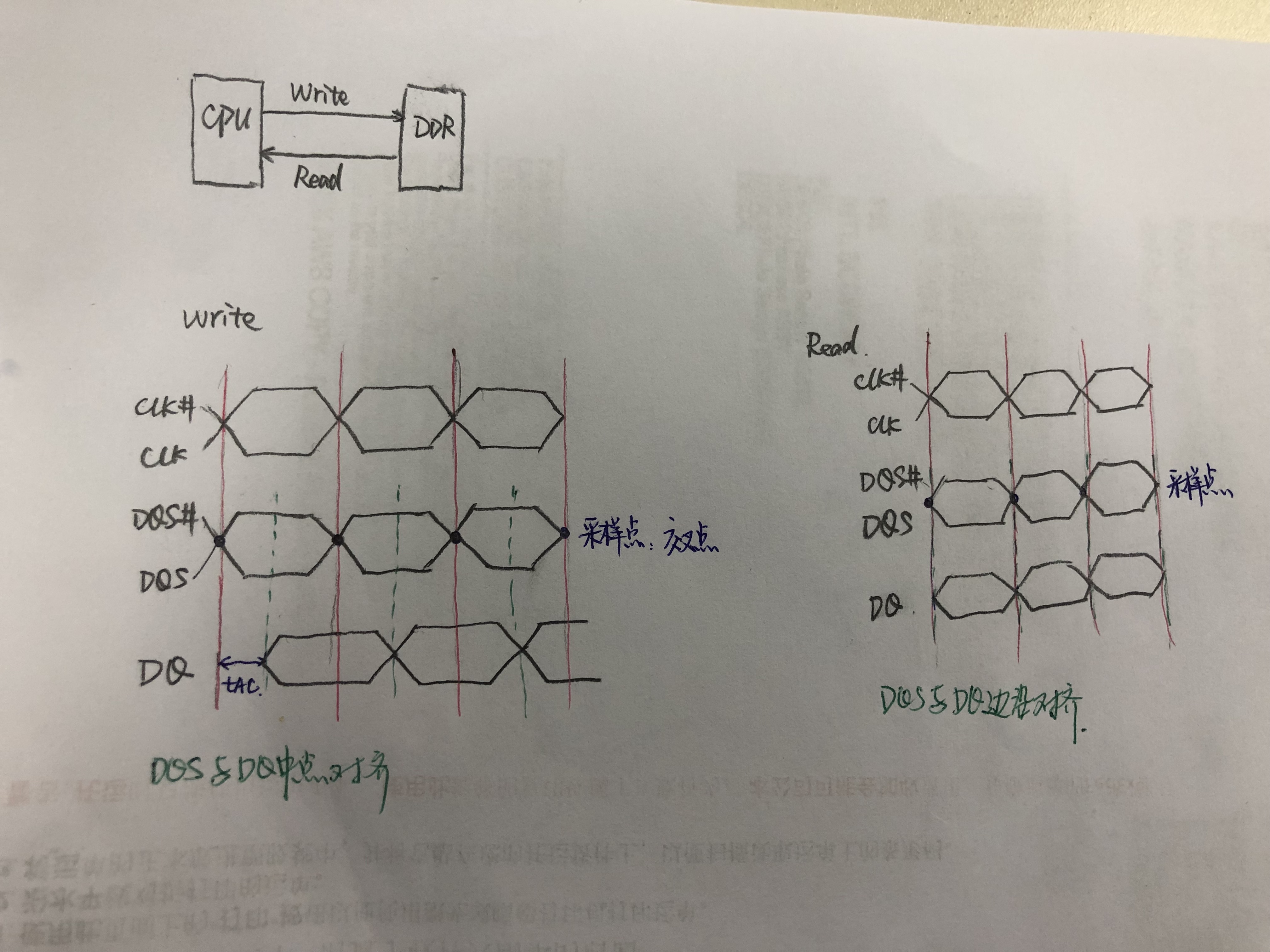

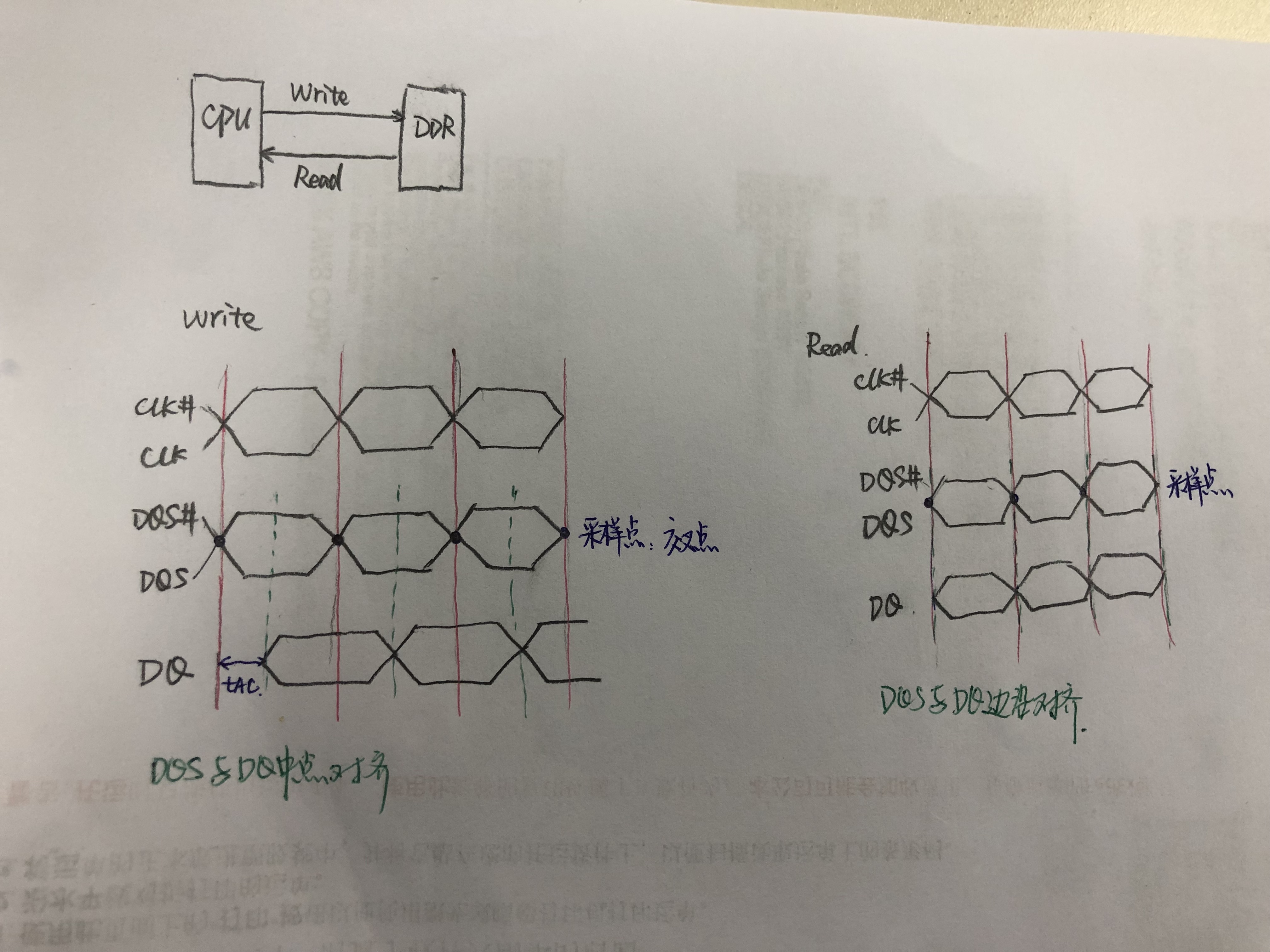

对DDR3来说,DQS与DQ的关系具体是怎样的?写是中间对齐,读是边沿对齐。这只是在说从波形上区分读写的方法吗?

无论读写,都是在DQS和DQS#的交差点采样数据的吗?如果是的话,写的时候,DQS和DQ一起从CPU发送至DDR,但是作为同步信号,为什么DQS和DQ存在一定的延迟?真的存在CPU内部的制御,为了保证足够的建立时间,会提前1/4周期发送DQ,促使DQS与DQS#的交差点和DQ的中间稳定电平对齐,从而使得在DQS与DQS#的交差点采样到稳定的DQ电平吗?但是当DDR侧发送数据至CPU的时候,DQS与DQS#的交差点和DQ的边沿对齐,那如果是在DQS和DQS#的交差点采样数据的话,CPU怎么能读取到稳定正确的数据呐?看时序的话,感觉采样到的都是中间电平啊?请大神指导一下啊

发帖

发帖 与我相关

与我相关 我的任务

我的任务 分享

分享