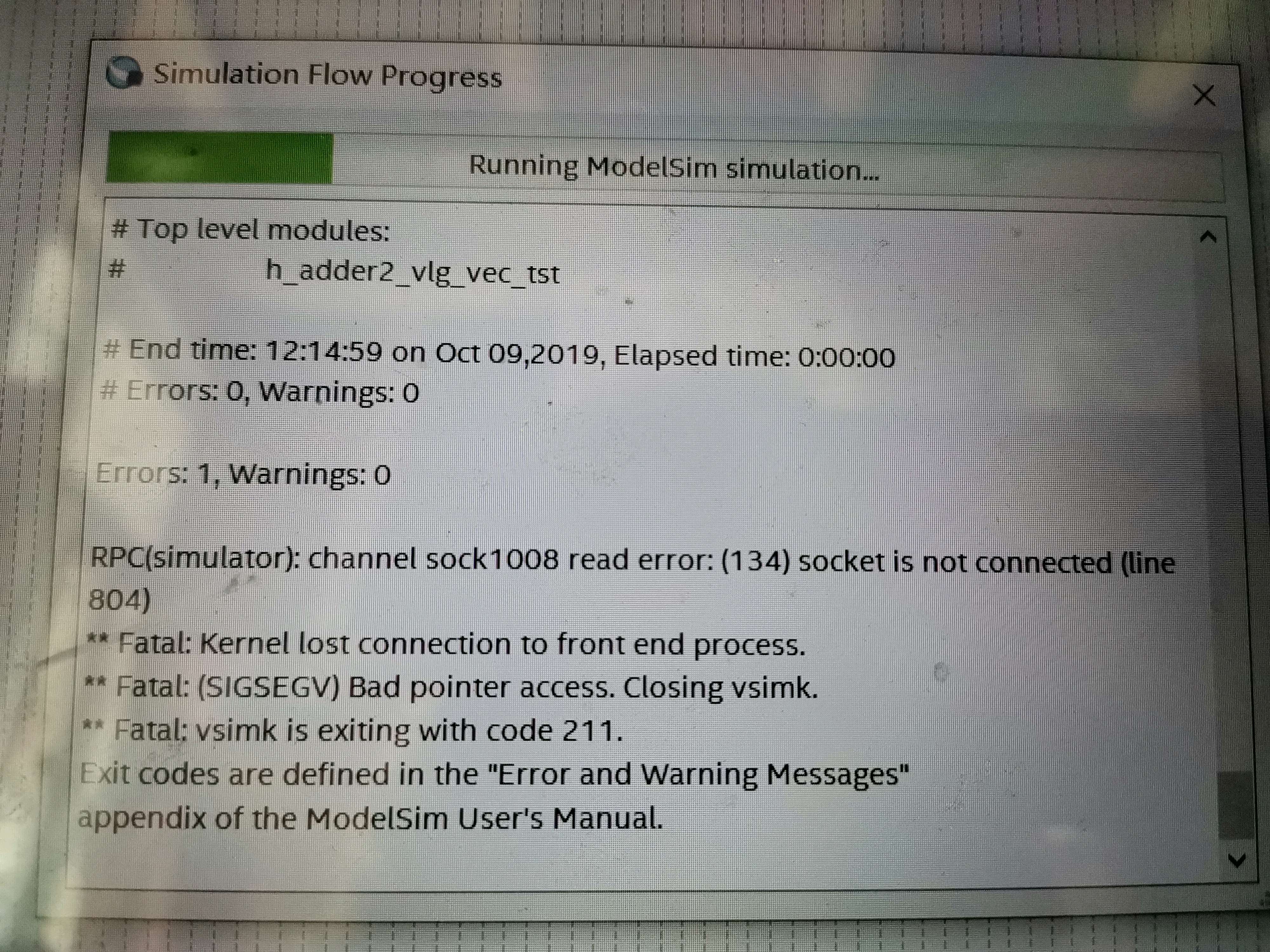

quarter 软件仿真时一直显示Runing ModelSim simulation,波形一直出不来,求大佬解答。

Determining the location of the ModelSim executable...Using: e:/intelfpga/17.1/modelsim_ase/win32aloem/To specify a ModelSim executable directory, select: Tools -> Options -> EDA Tool OptionsNote: if both ModelSim-Altera and ModelSim executables are available, ModelSim-Altera will be used.**** Generating the ModelSim Testbench ****quartus_eda --gen_testbench --tool=modelsim_oem --format=verilog --write_settings_files=off h_adder2 -c h_adder2 --vector_source="E:/Study Source/source/EDA/project2/Waveform.vwf" --testbench_file="E:/Study Source/source/EDA/project2/simulation/qsim/Waveform.vwf.vt"Info: *******************************************************************Info: Running Quartus Prime EDA Netlist Writer Info: Version 17.1.0 Build 590 10/25/2017 SJ Standard Edition Info: Copyright (C) 2017 Intel Corporation. All rights reserved. Info: Your use of Intel Corporation's design tools, logic functions Info: and other software and tools, and its AMPP partner logic Info: functions, and any output files from any of the foregoing Info: (including device programming or simulation files), and any Info: associated documentation or information are expressly subject Info: to the terms and conditions of the Intel Program License Info: Subscription Agreement, the Intel Quartus Prime License Agreement, Info: the Intel FPGA IP License Agreement, or other applicable license Info: agreement, including, without limitation, that your use is for Info: the sole purpose of programming logic devices manufactured by Info: Intel and sold by Intel or its authorized distributors. Please Info: refer to the applicable agreement for further details. Info: Processing started: Wed Oct 09 12:14:52 2019Info: Command: quartus_eda --gen_testbench --tool=modelsim_oem --format=verilog --write_settings_files=off h_adder2 -c h_adder2 --vector_source="E:/Study Source/source/EDA/project2/Waveform.vwf" --testbench_file="E:/Study Source/source/EDA/project2/simulation/qsim/Waveform.vwf.vt"Info (119006): Selected device 5CGXFC7C7F23C8 for design "h_adder2"Warning (18236): Number of processors has not been specified which may cause overloading on shared machines. Set the global assignment NUM_PARALLEL_PROCESSORS in your QSF to an appropriate value for best performance.Completed successfully. Completed successfully. **** Generating the functional simulation netlist ****quartus_eda --write_settings_files=off --simulation --functional=on --flatten_buses=off --tool=modelsim_oem --format=verilog --output_directory="E:/Study Source/source/EDA/project2/simulation/qsim/" h_adder2 -c h_adder2Info: *******************************************************************Info: Running Quartus Prime EDA Netlist Writer Info: Version 17.1.0 Build 590 10/25/2017 SJ Standard Edition Info: Copyright (C) 2017 Intel Corporation. All rights reserved. Info: Your use of Intel Corporation's design tools, logic functions Info: and other software and tools, and its AMPP partner logic Info: functions, and any output files from any of the foregoing Info: (including device programming or simulation files), and any Info: associated documentation or information are expressly subject Info: to the terms and conditions of the Intel Program License Info: Subscription Agreement, the Intel Quartus Prime License Agreement, Info: the Intel FPGA IP License Agreement, or other applicable license Info: agreement, including, without limitation, that your use is for Info: the sole purpose of programming logic devices manufactured by Info: Intel and sold by Intel or its authorized distributors. Please Info: refer to the applicable agreement for further details. Info: Processing started: Wed Oct 09 12:14:54 2019Info: Command: quartus_eda --write_settings_files=off --simulation=on --functional=on --flatten_buses=off --tool=modelsim_oem --format=verilog --output_directory="E:/Study Source/source/EDA/project2/simulation/qsim/" h_adder2 -c h_adder2Info (119006): Selected device 5CGXFC7C7F23C8 for design "h_adder2"Warning (18236): Number of processors has not been specified which may cause overloading on shared machines. Set the global assignment NUM_PARALLEL_PROCESSORS in your QSF to an appropriate value for best performance.Info (204019): Generated file h_adder2.vo in folder "E:/Study Source/source/EDA/project2/simulation/qsim//" for EDA simulation toolInfo: Quartus Prime EDA Netlist Writer was successful. 0 errors, 1 warning Info: Peak virtual memory: 4725 megabytes Info: Processing ended: Wed Oct 09 12:14:56 2019 Info: Elapsed time: 00:00:02 Info: Total CPU time (on all processors): 00:00:02Completed successfully. **** Generating the ModelSim .do script ****E:/Study Source/source/EDA/project2/simulation/qsim/h_adder2.do generated.Completed successfully. **** Running the ModelSim simulation ****e:/intelfpga/17.1/modelsim_ase/win32aloem//vsim -c -do h_adder2.doReading E:/intelFPGA/17.1/modelsim_ase/tcl/vsim/pref.tcl# 10.5b# do h_adder2.do# ** Warning: (vlib-34) Library already exists at "work".# Model Technology ModelSim - Intel FPGA Edition vlog 10.5b Compiler 2016.10 Oct 5 2016# Start time: 12:14:58 on Oct 09,2019# vlog -work work h_adder2.vo # -- Compiling module h_adder2# # Top level modules:# h_adder2# End time: 12:14:59 on Oct 09,2019, Elapsed time: 0:00:01# Errors: 0, Warnings: 0# Model Technology ModelSim - Intel FPGA Edition vlog 10.5b Compiler 2016.10 Oct 5 2016# Start time: 12:14:59 on Oct 09,2019# vlog -work work Waveform.vwf.vt # -- Compiling module h_adder2_vlg_vec_tst# # Top level modules:# h_adder2_vlg_vec_tst# End time: 12:14:59 on Oct 09,2019, Elapsed time: 0:00:00# Errors: 0, Warnings: 0Errors: 1, Warnings: 0RPC(simulator): channel sock1008 read error: (134) socket is not connected (line 804)** Fatal: Kernel lost connection to front end process.** Fatal: (SIGSEGV) Bad pointer access. Closing vsimk.** Fatal: vsimk is exiting with code 211.Exit codes are defined in the "Error and Warning Messages"appendix of the ModelSim User's Manual.

发帖

发帖 与我相关

与我相关 我的任务

我的任务 分享

分享