69

社区成员

发帖

发帖 与我相关

与我相关 我的任务

我的任务 分享

分享目录:

一、什么是信号串扰

1、概述

2、容性耦合

3、感性耦合

二、具体案例分析

1、RS485发射端串扰

1)本文摘要 2)问题发现及解决过程 3)解决方法

2、1MHz四线SPI通信串扰

------------------------------------------------------------------------------------------------------------------------

一、什么是信号串扰

1、概述

串扰指的是在两条信号线之间的耦合现象。信号因为空间距离近的原因导致的信号线之间会出现不希望看到的电感性和电容性耦合从而互相干扰。电容性耦合会引发耦合电流,而电感性耦合则引发耦合电压。在电路设计中,是一个比较棘手的问题。

------------------------------------------------------------

2、容性耦合

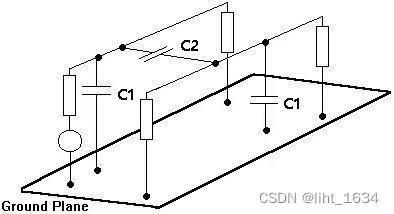

回忆一下我们所熟悉的平行板电容,两个规则平行板导体,周围充满介质就形成了一个电容器。对于 PCB 板上的情况,两条走线之间和参考平面之间也会形成电容器,C1 表示走线和参考平面之间形成的电容,C2 表示两走线之间形成的电容。从电容的角度来看,当一条走线上电压变化时,相当于电容 C2 两端电压变化,电容 C2 充电邻近的导体(电容的另一端)上必然也会有电流,串扰随之产生。走线之间的电容与走线之间的间距密切相关,当间距增大时,耦合电容迅速减小,耦合作用急剧减弱。

图1.2.1 容性耦合(Capacitive coupling)

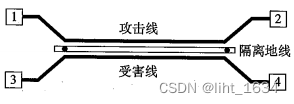

如果在两条走线之间放入另一根走线,这两跳走线之间耦合电容会进一步减小,这种现象正是使用隔离地线抑制串扰的出发点之一。

图1.2.2

------------------------------------------------------------

3、感性耦合

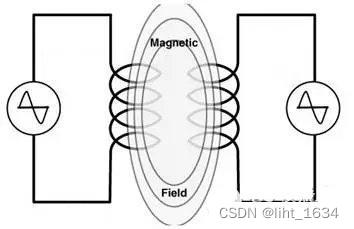

如果一条走线上有数字信号传输,在信号电平跳变过程中,即信号处于跳变边沿时,走线上电压不断变化,走线上的电流也不断变化,这样在走线周围产生变化的磁场,而变化的磁场在邻近走线上产生感应电流。这就是感性耦合。同样的拉开 PCB 板上走线的间距,能明显减小两天线之间的互感耦合。

图1.3.1 感性耦合(InducTIve coupling)

------------------------------------------------------------------------------------------------------------------------

二、具体案例分析

1、RS485发射端串扰的解决

1)本文摘要

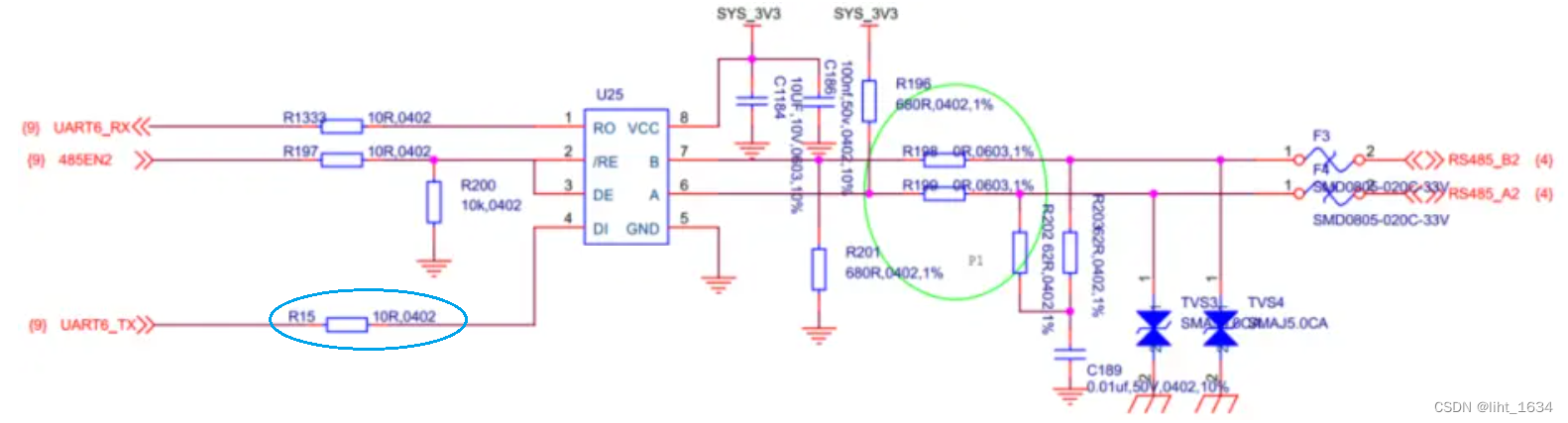

本文要解决的是RS485发送端波形噪声干扰大的问题,如下图1所示是其原理图,RS485的发送、接收、使能控制引脚通过一个10R电阻分别直接连接到MCU端口上。这个电路是目前市面上比较常用的RS485方案,具体的实现方式如下:

在空闲期间,485EN为低电平,MCU处于接收状态;在准备发送数据之前,MCU会先拉高485EN,U25处于发送状态;发送完毕之后,485EN重新处于低电平,U25处于接收状态。此方案的关键是要掌握好控制485EN引脚的高低的时机,否则会有丢包问题。

图2.1.1 RS485 典型应用原理图

---------------------------------

2)问题发现及解决过程

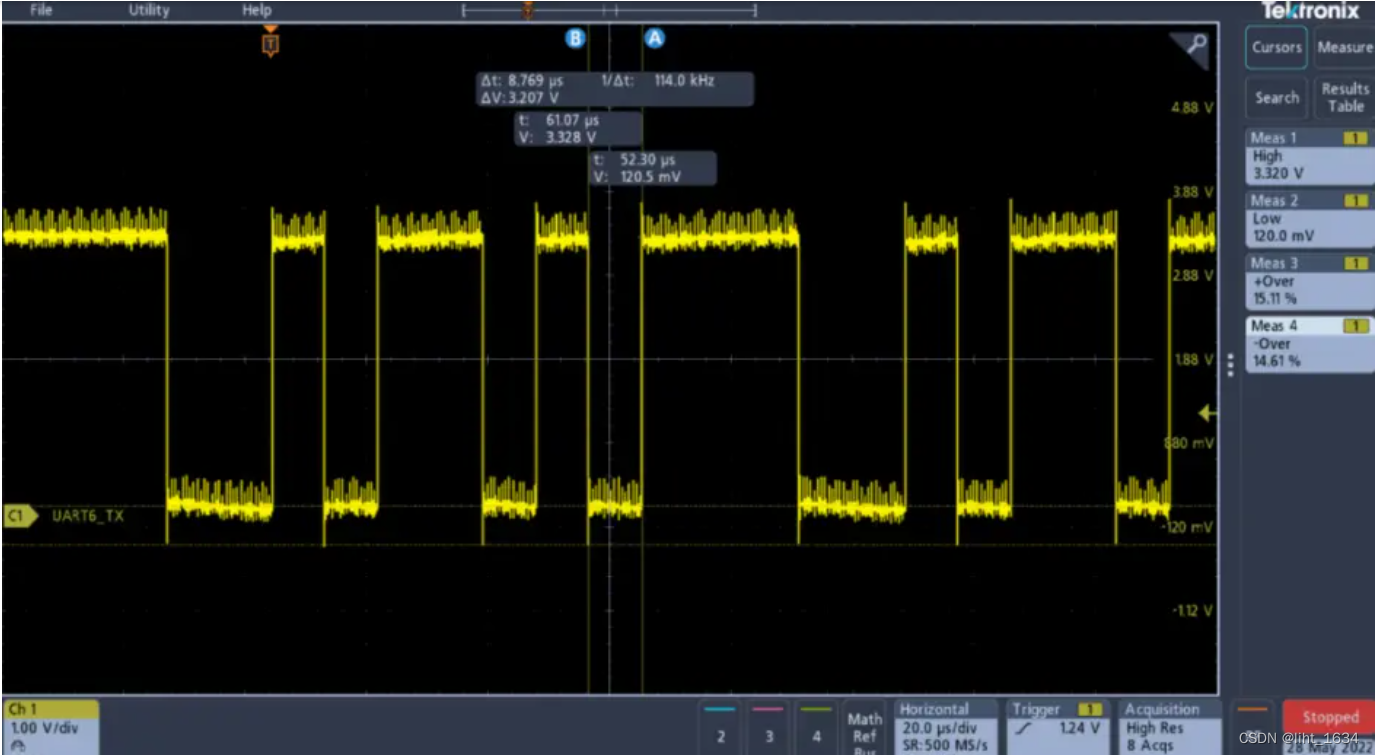

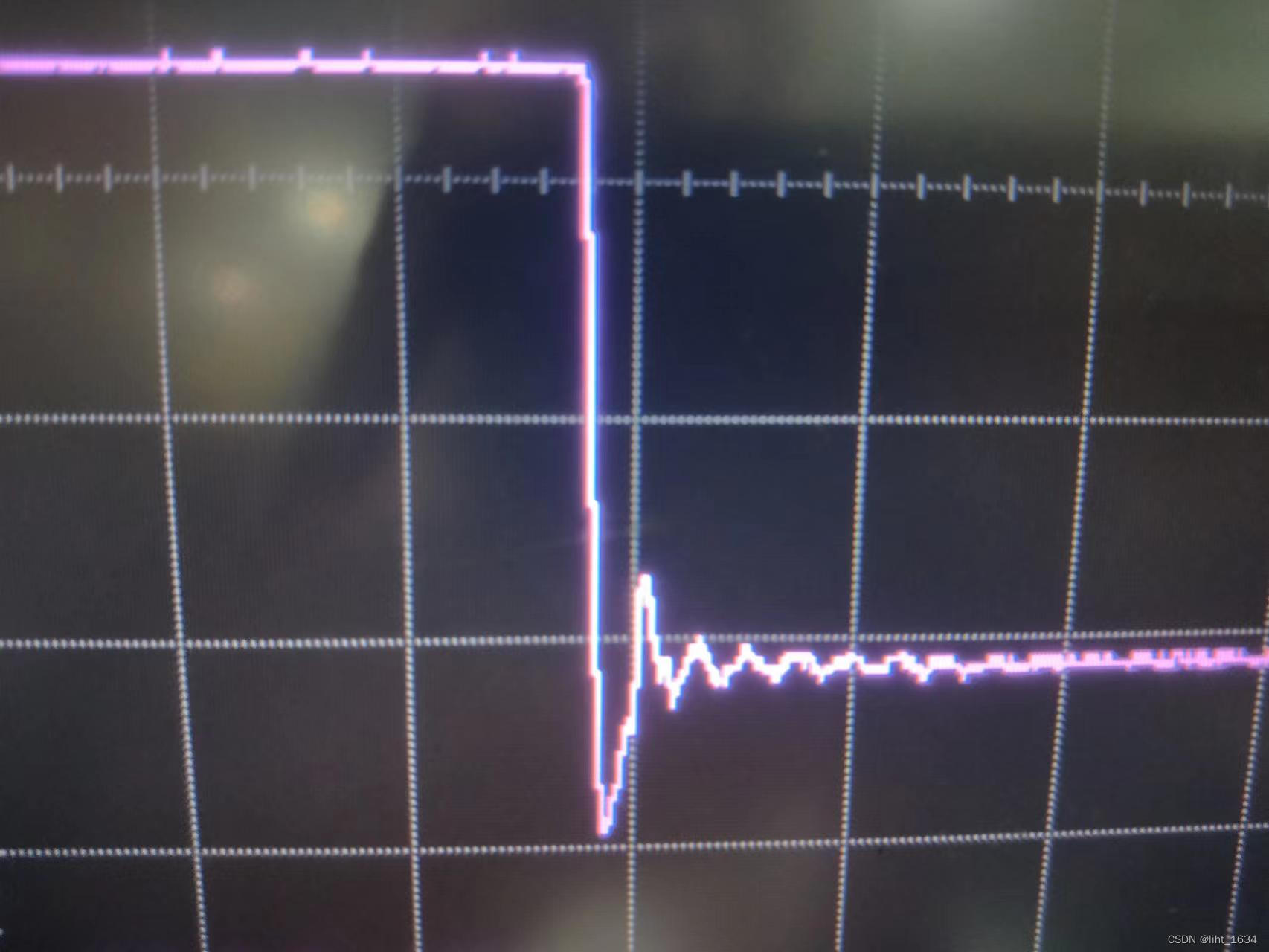

硬件测试时发现发射端DI的波形如下图2所示,在信号上有很大的毛刺(电阻R15前后都一样,图1蓝色圈),测量另外一路同样的RS485电路就不会有这种问题,分析电路原理上是不会有问题的,怀疑是这路信号被其他信号干扰了。

图2.1.2 RS485发射引脚DI(UART6_TX)的波形图

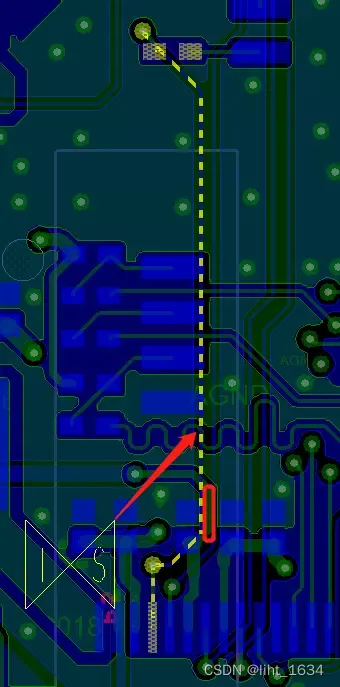

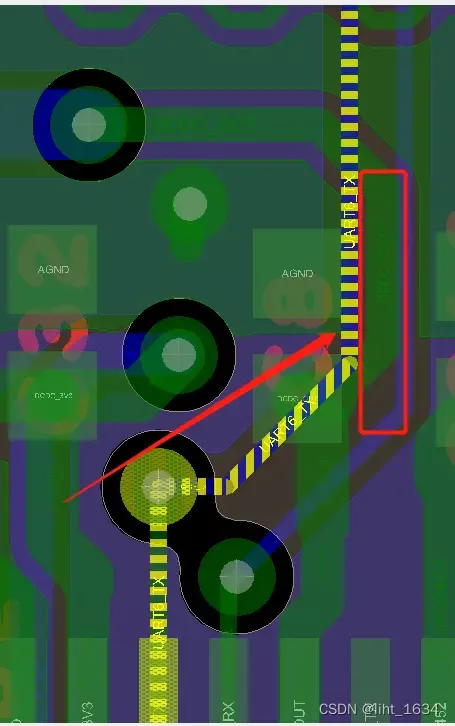

打开PCB图,找到UART6_TX这根线对应的PCB走线图,如下图3、图4所示。我们可以看到这根线从MCU出来后通过过孔到第三层,然后径直往上,在上面通过过孔回到第一层,然后通过R15电阻接入RS485芯片的DI引脚,整个路径除了和第一层的DCDC_OUT这根线有一段短距离的平行布线之外,其余还算干净。查看DCDC_OUT信号,发现DCDC_OUT是MCU的内核电压,系统选用的MCU内部含有PMU单元,内部DCDC单元是其中的一部分,其框图如下图5所示。考虑到buck芯片的强干扰影响,猜测是内核DCDC输出布线对UART6_TX造成的耦合干扰。不在同一层平行走线往往这种耦合干扰更严重。

图2.1.3 UART6_TX走线路径图

图2.1.4 UART6_TX与DCDC_OUT平行走线部分

图2.1.5 DCDC block diagram

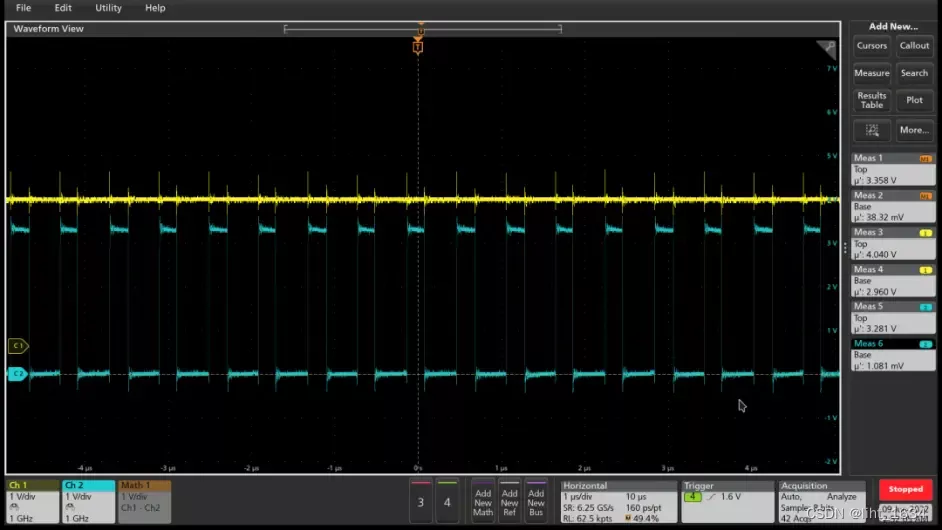

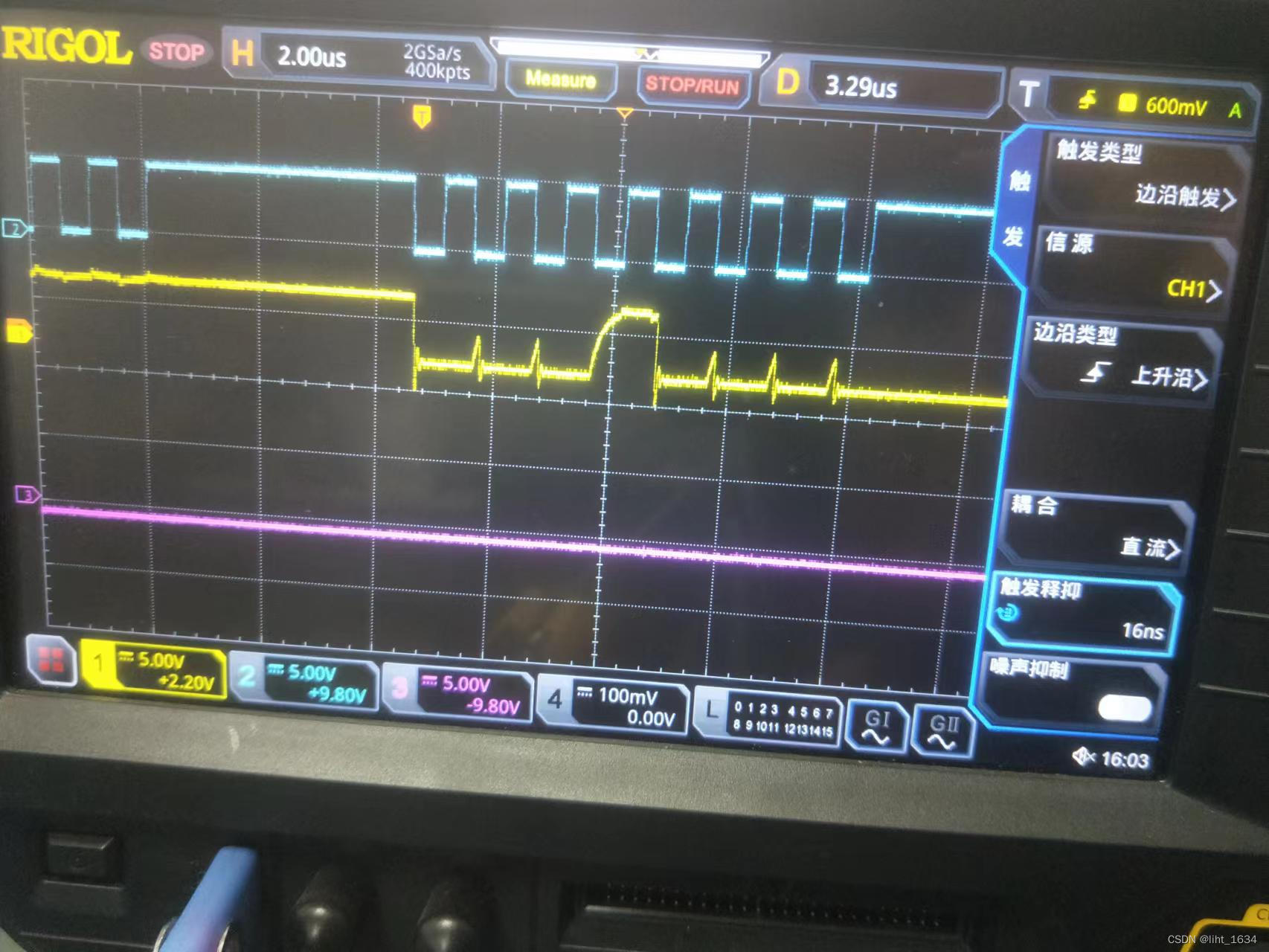

同时监测RS485发送引脚波形DI与LP点(图5框图中电感前)的电压波形,如下图6所示,可以发现,干扰的频率与LP处频率基本一致,基本可以判断是芯片内核电源buck芯片的平行输出布线耦合到RS485 DI引脚上去的。

注:黄色代表RS485上波形,蓝色代表LP处波形

图2.1.6 发送端DI与LP处波形

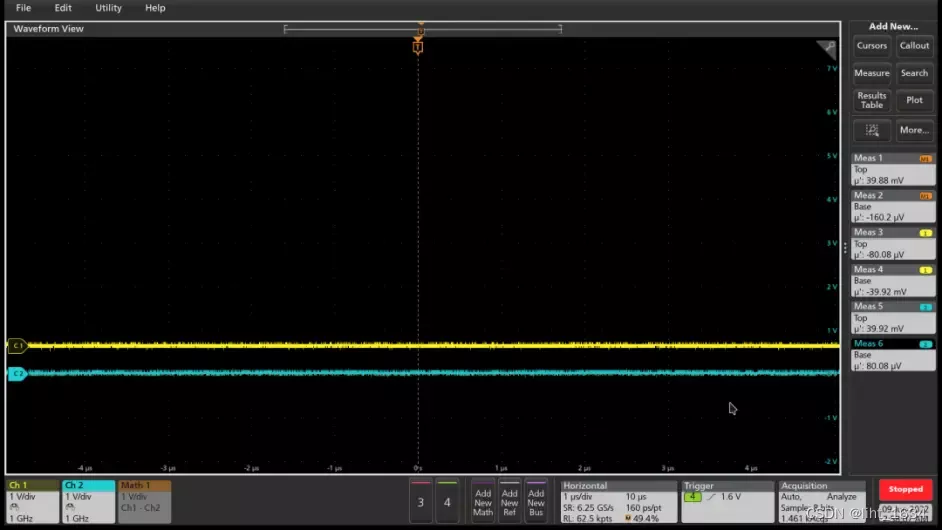

那有人说了,这样判断是不是有点草率了?有没有可能是RS485芯片部分的接收到其他地方的干扰传导前面发射端的呢?好的,那我们再来验证一下:我们先把R15电阻断开,然后观测靠近MCU端的波形和LP点输出电压波形,如下如7所示,发现断开R15后,干扰波形依然存在,测量DI端波形,如下图8所示,波形无干扰。因此,基本确定干扰由前级DCDC_OUT与UART6_TX平行布线部分串进来的。

图2.1.7 R15断开后测量的MCU端与LP处波形

图2.1.8 R15断开后测量DI端波形(黄色)

---------------------------------

3)解决方法

原因找到了,那么如何去除干扰呢?

(1)布线的时候将这段平行布线改掉,避免平行布线或拉远布线间距;

(2)RS485发送DE引脚加一个小电容滤除噪声,因为噪声频率在1.65MHz,RS485频率最大110k,频率相差比较大,好滤除。如下是在DI引脚处添加不同容值的电容时的测试波形图,考虑到既要去除干扰又要保证信号波形上升下降沿的质量,因此最终选择用1nF电容。

图2.1.9 22pF时DI引脚波形图

图2.1.10 220pF时DI引脚波形图

图2.1.11 1nF时DI引脚波形图

图2.1.12 10nF时DI引脚波形图

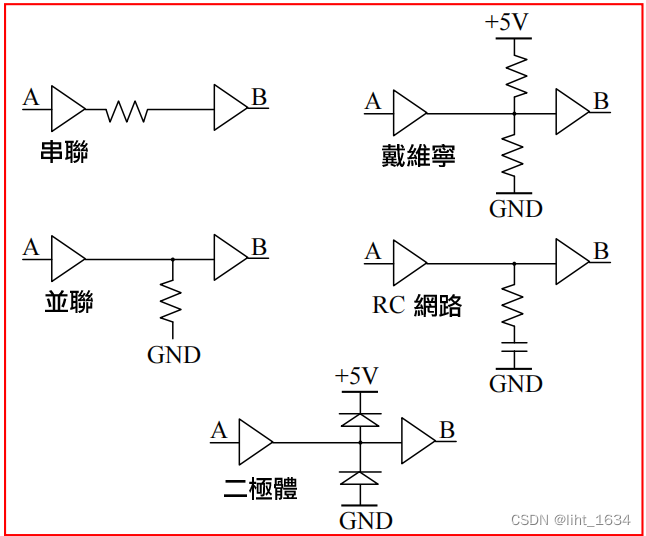

另外减少SI之串扰的常用方法是在传输线上增加端接器件,常用终端形式如下图,百度网盘搜索“EMC_Layout P76”。

图2.1.13 终端(Termination)形式

-----------------------------------------------------------

2、1MHz四线SPI通信串扰

1)硬件电路

①高速信号的判定:电源、信号完整性与高速电路-CSDN博客。

②信号线和时钟线串电阻:高速信号一般在电路的终端串接小电阻用于阻抗的匹配,TTL信号阻抗约13,串接33Ω即可,防信号完整性问题。另可参见:附录1、小小串联电阻,大大的作用。

③测试电路:Arduino基础与进阶之四、Arduino实验之10、实战库仑计(电池电量计)中的DC2026C与LTC6820之间采用4线SPI。

---------------------------------

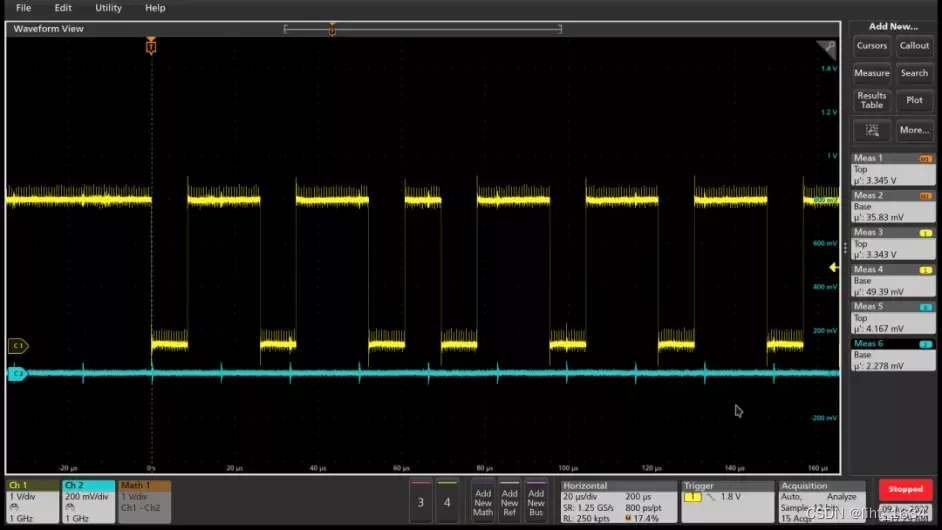

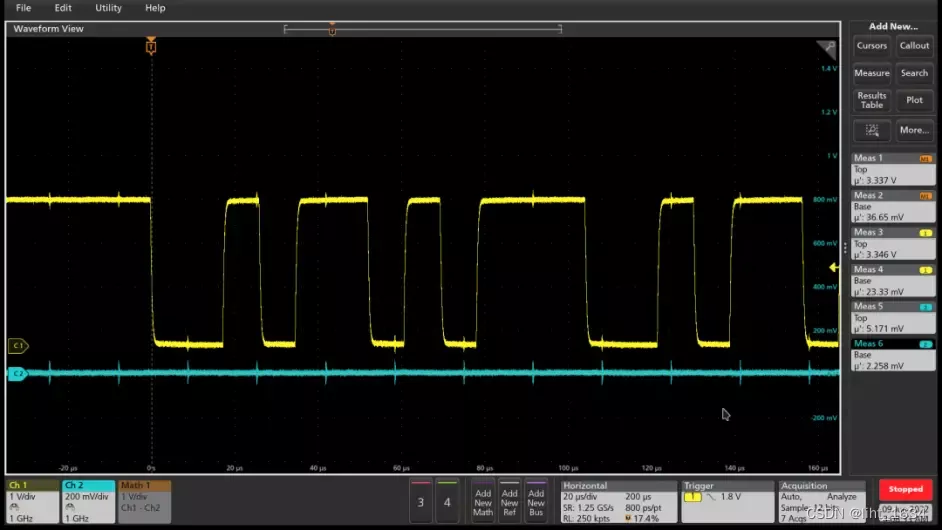

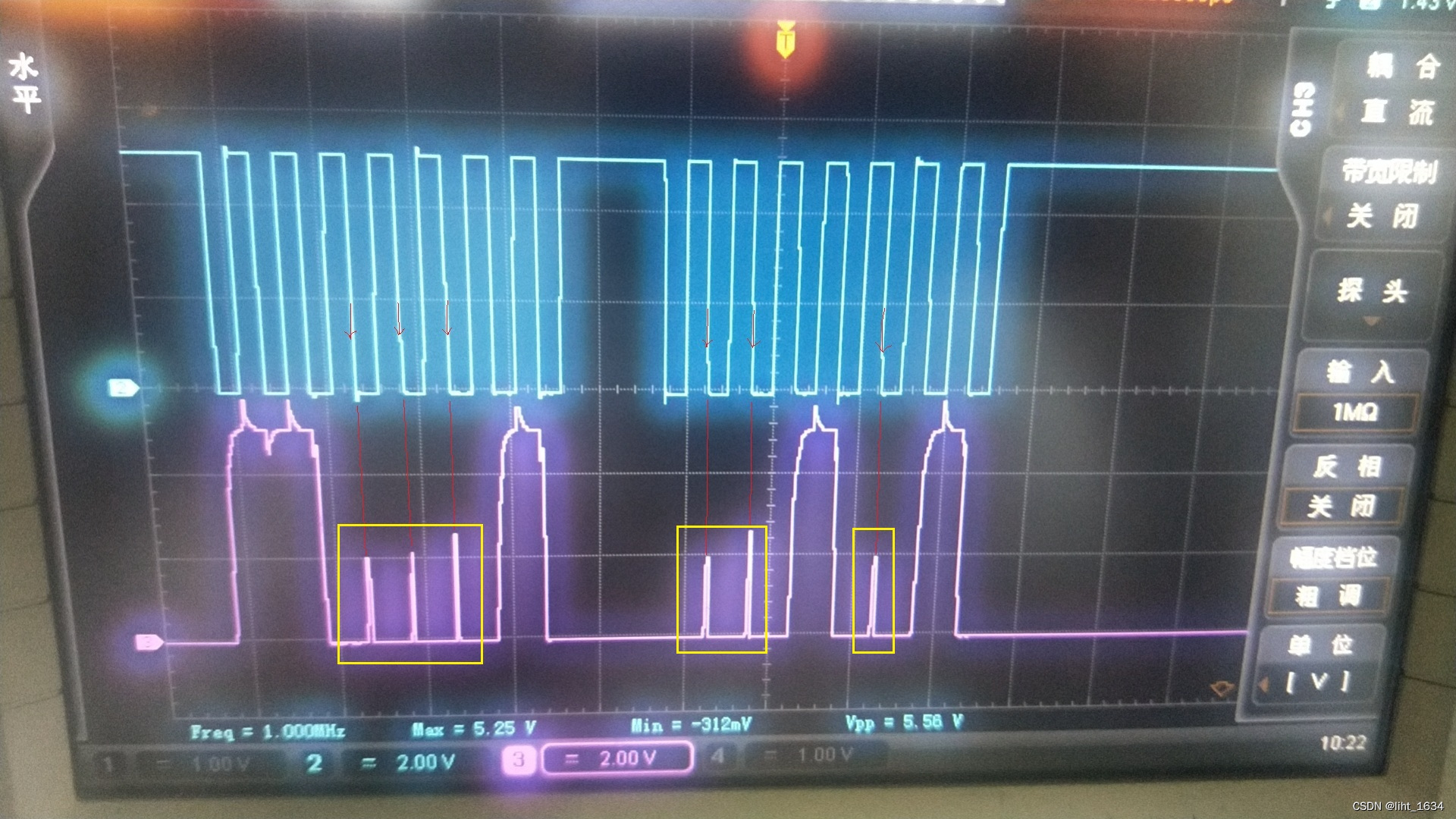

2)1MHz SPI传输问题

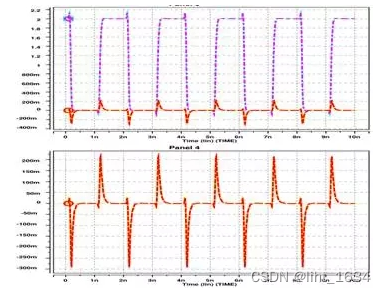

蓝色SCK、紫色或黄色MISO,如下图所示。SCK下降沿时,MISO有过冲且振铃。 这是一个强烈的EMI源。

降低传输速率至500KHz,过冲基本消失。初步判断为串扰所致。

MISO串联电阻:

尝试硬件解决,无果。固件上在SCK上升沿采样MISO,即可规避过冲的影响。

------------------------------------------------------------------------------------------------------------------------