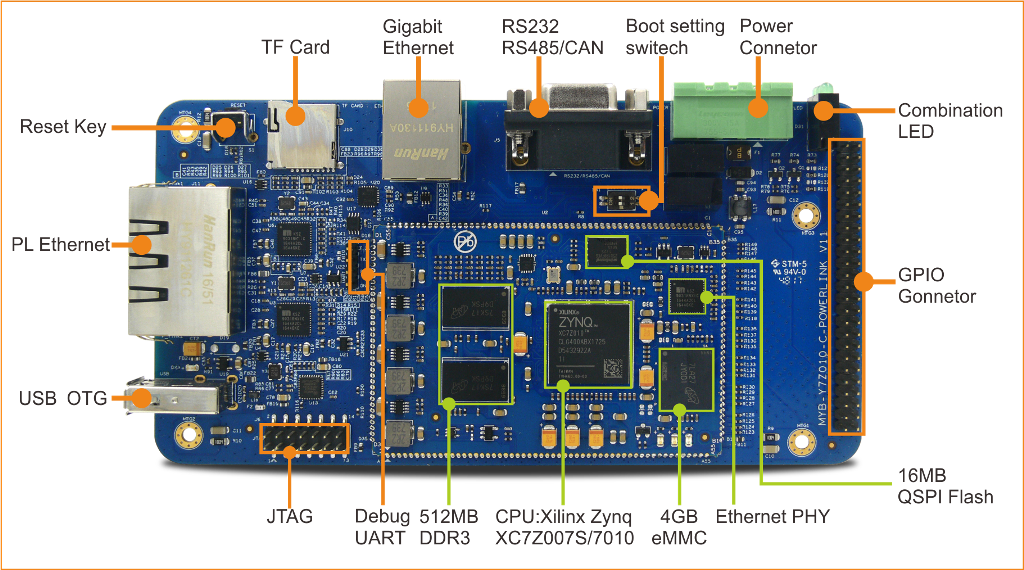

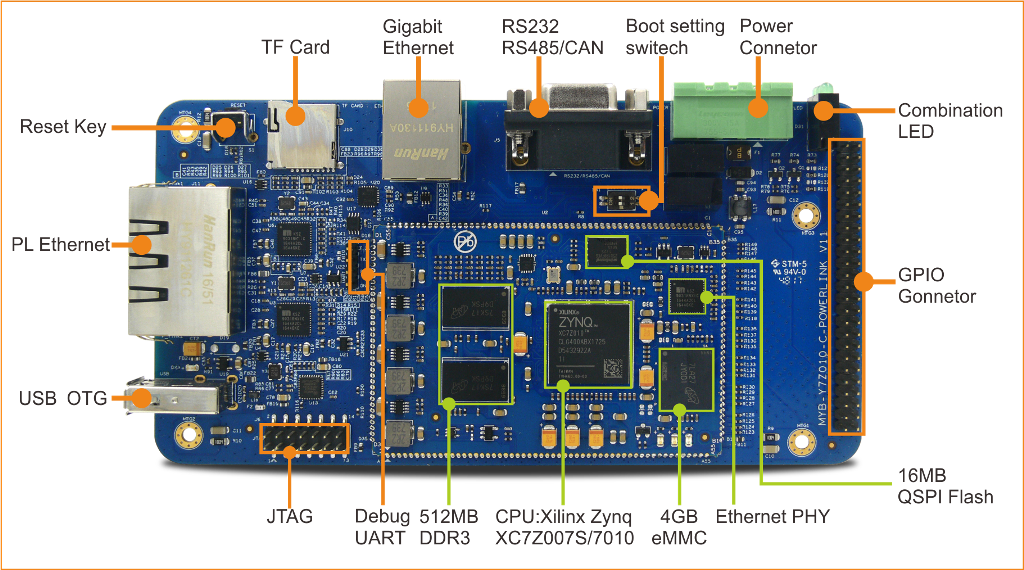

硬件:MYD-Y7Z010/007S开发板

简介:MYD-Y7Z010/007S开发板由MYC-Y7Z010/007S核心板加MYB-Y7Z010/007S底板组成。核心板采用了Xilinx最新的基于28nm工艺的Zynq-7000 All Programmable SoC平台,集成了单/双核ARM Cortex-A9处理器和FPGA,具有高性能,低功耗,高扩展等特性,能在工业设计中满足各种需要。底板搭载以太网口,USB 2.0接口,TF卡接口,RS232,RS485,CAN等多种接口,方便评估或集成。开发板采用Linux,提供包括用户手册,PDF底板原理图,外扩接口驱动,BSP源码包,开发工具等,为开发者提供了完善的软件开发环境,帮助降低产品开发周期,实现产品快速上市。

接上一章继续介绍MYD-Y7Z010/007S开发板硬件资源:

3.4 存储

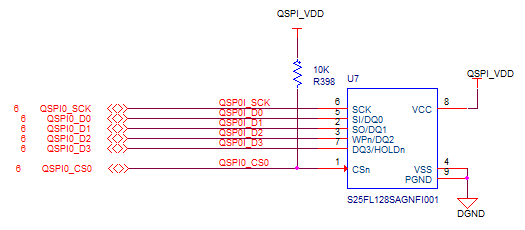

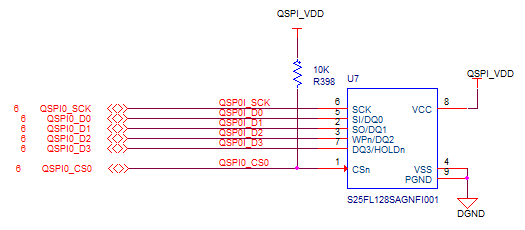

3.4.1 SPI Flash

核心板板载一片16MB QSPI Flash W25Q128FVEIG,可以用于引导SoC,初始化PS并配置PL部分。接口PS BANK500 MIO[1-6]。

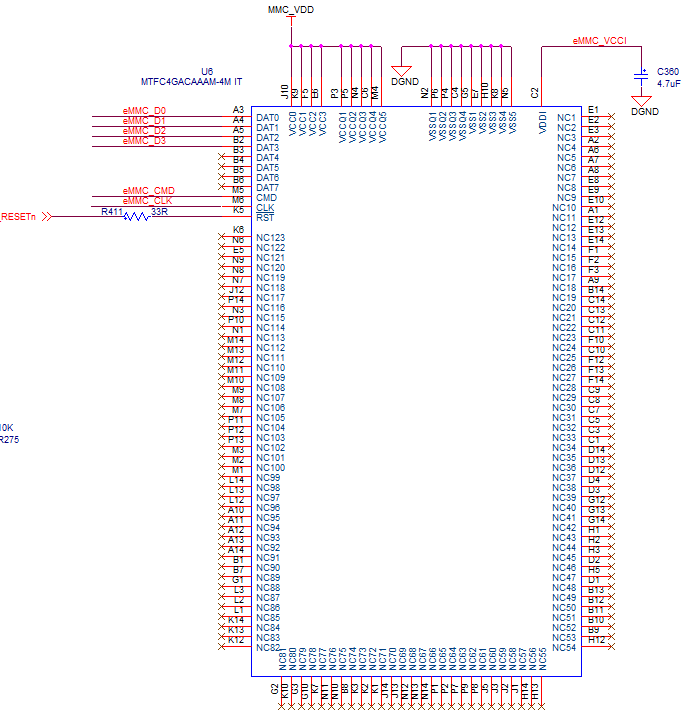

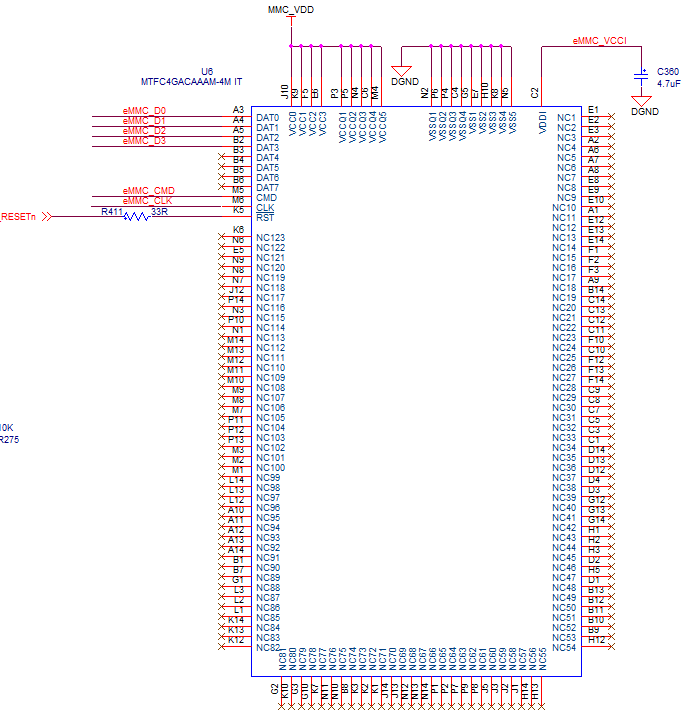

3.4.2 eMMC

开发板板载4GB MICRON EMMC,接口PS_SDIO1,可用于系统文件或其他数据文件存储。可用作次级启动设备,与QSPI FLASH一起用于系统启动。接口PS BANK500 MIO[10-15]。

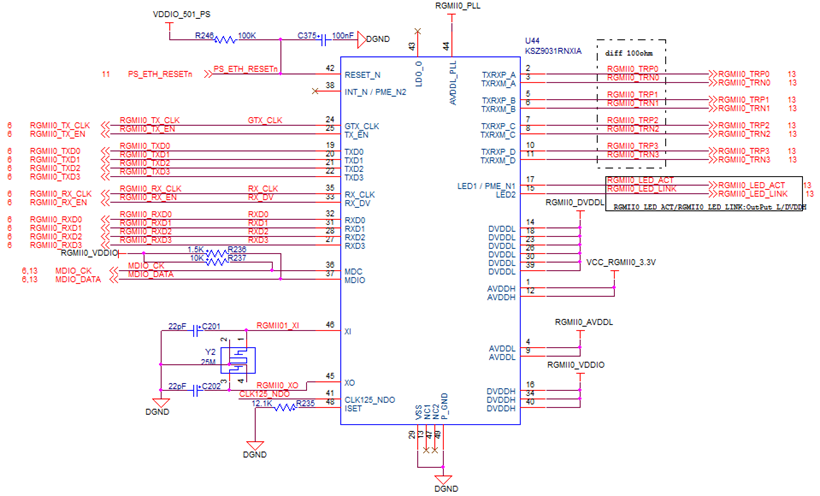

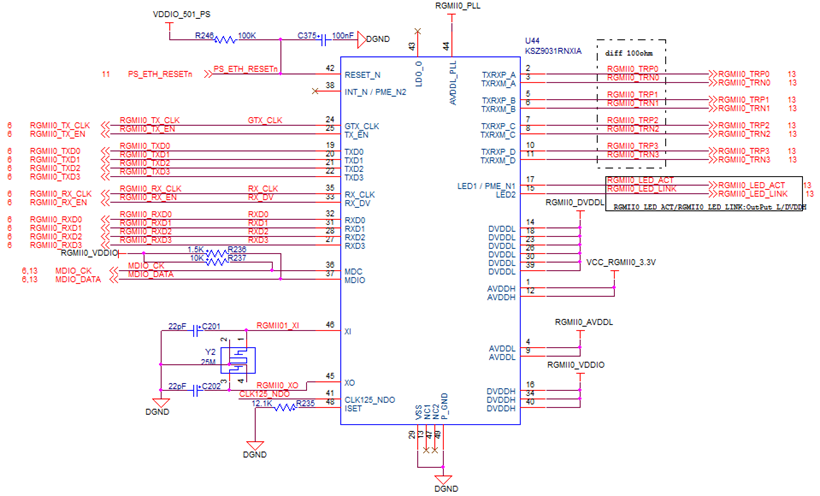

3.5 以太网

PS MAC0接口Ethernet PHY KSZ9031RN实现千兆网口。接口PS BANK501 MIO[16-27]。

3.6 USB

PS USB1控制器外接PHY USB3320可实现USB OTG。接口PS BANK MIO[28-39]。

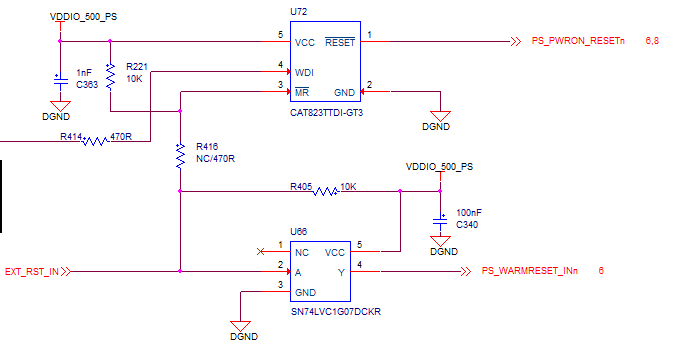

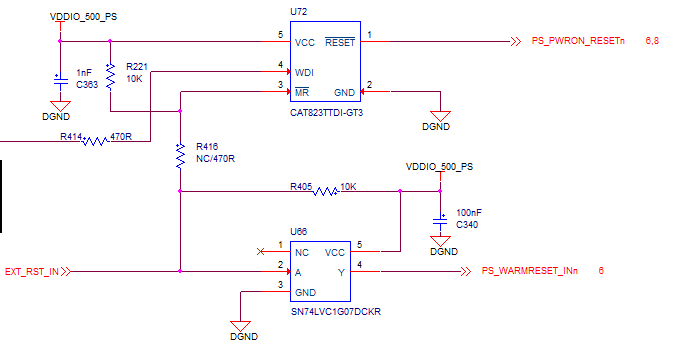

3.7看门狗及复位相关配置

使用外部看门狗芯片CAT823TTDI-GT3,该芯片的喂狗引脚连接到了CPU的PS_MIO0引脚,WDI未短接时看门狗不工作,调试阶段可以通过跳线禁止看门狗工作。

第4章 硬件接口

4.1 板上接口说明

编号 说明

J1 电源座子

J4,J11 以太网座子(1PS以太网 + 2PL Ethernet)

J5 DB9母座 (RS232/RS485/CAN)

J6 JTAG座子

J7 50Pin 2.54mm间距插针

J8 3.3V UART插针

J9 USB 接口

J10 TF卡接口

D31 组合LED灯

SW1 启动配置开关

S1 复位按键

4.2 PS单元接口

4.2.1 以太网

1路10/100/1000Mbps以太网接口,PHY芯片集成在核心板上,由底板上的RJ45端口J4引出。

4.2.2 USB

1路USB 2.0 高速接口,由底板板载USB Phy USB3320c实现,端口为J9。

4.2.3 CAN/RS232/RS485

CAN/RS232/RS485各一路经由DB9接口J5引出。

4.2.4 调试串口

1路3.3V UART接口,作为系统默认调试串口,端口为J8。

4.2.5 按键

一个复位按键S1用于系统复位。

4.2.6 JTAG

1路14 Pin JTAG接口,可用于PS和PL调试,端口为J6。

4.2.7 TF卡

1路TF卡接口J10。

4.3 PL单元接口

4.3.1 PL Ethernet

两路由PL扩展的标准以太网接口。

4.3.2 GPIO插针

GPIO插针可用于其他应用扩展。

本章到此结束,下一章继续介绍linux的软件资源

发帖

发帖 与我相关

与我相关 我的任务

我的任务 分享

分享