4,575

社区成员

发帖

发帖 与我相关

与我相关 我的任务

我的任务 分享

分享存储器是现代信息系统最关键的组件之一,已经形成主要由DRAM与NAND Flash构成的超千亿美元的市场。随着万物智联时代的到来,人工智能、智能汽车等新兴应用场景对存储提出了更高的性能要求,促使新型存储器迅速发展,影响未来存储器市场格局。

我们聚焦于新型存储器中的阻变存储器 (ReRAM或RRAM,Resistive RAM),并通过分析其技术、应用场景与模式,得出如下判断:

(1). 万物智联时代,需要速度、功耗、容量等性能更强的新型存储器;

(2). 对比四大新型存储器,ReRAM在密度、工艺制程、成本和良率上具备明显优势;

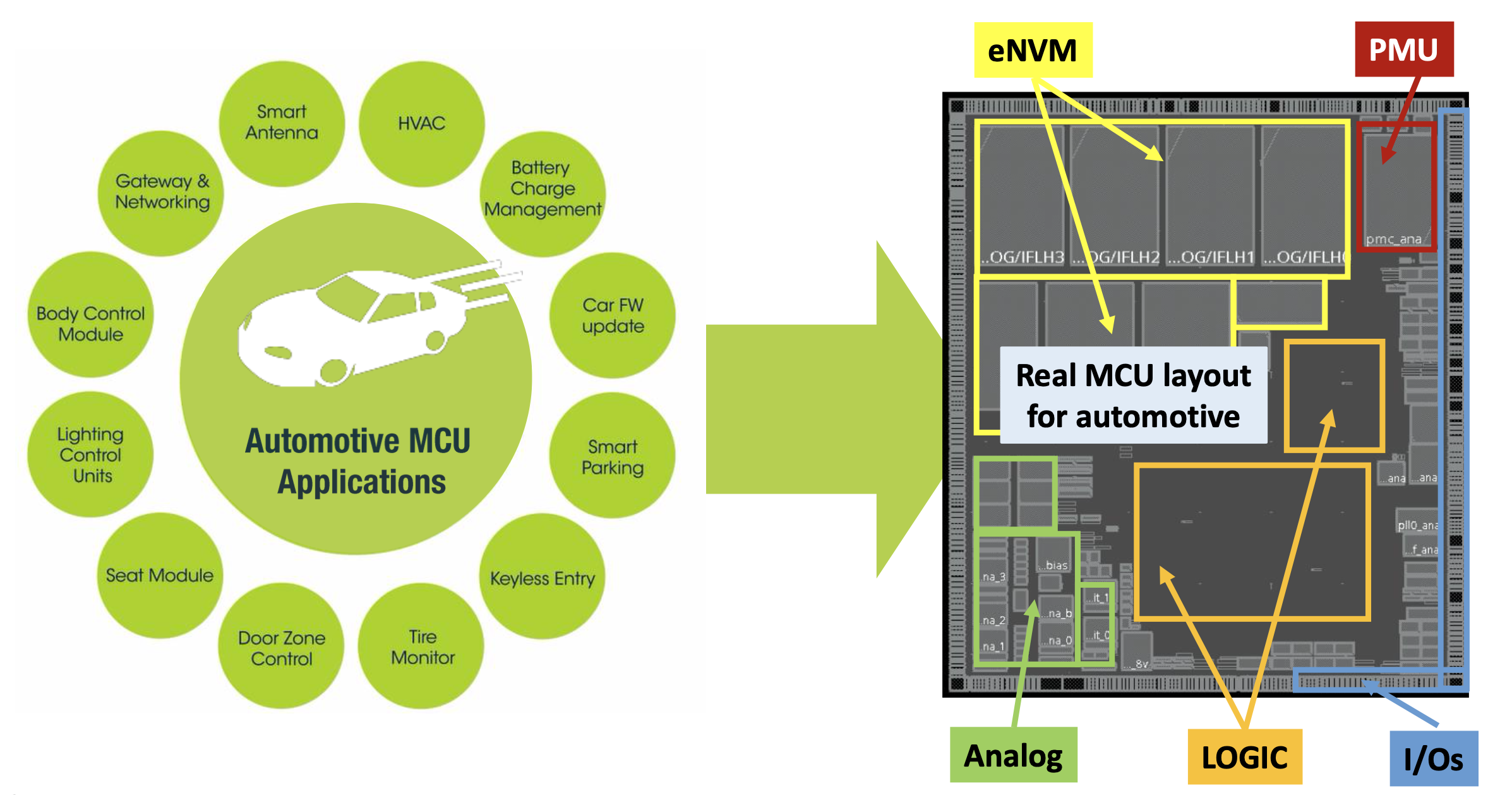

(3). AIoT、智能汽车、数据中心、AI计算(存算一体)将是ReRAM的重要发展机遇;

(4). IDM模式是ReRAM厂商的最佳选择;

(5).新型存储器是中国实现存储领域弯道超车的最佳机会。

超大规模集成电路(VLSI)工业跟上高密度步伐的一种可能方式,计算能力和能源效率是在二进制逻辑之前研究一些技术。最近多年来,多值逻辑(MVL)引起了数字系统设计者的注意。碳纳米管场效应晶体管(CNTFET)已经专门用于实现MVL电路。

电阻式随机存取存储器(RRAM)由于其功能,为执行MVL提供了一种非常耐用的选择将各种电阻状态存储在一个单元中。互补金属氧化物半导体(CMOS)器件在较低技术下面临的器件退化和可靠性问题节点迫使研究人员寻找替代技术。

研究人员不时地指出二进制逻辑,尤其是在互连复杂性方面。互连贡献了70%的有源芯片面积,从而有助于片上功耗的主要来源。此外,的配额在今天的情况下,在特定时刻进行二进制数据传输是不够的数据匮乏的系统。克服二进制提供的限制逻辑上,重点转移到了MVL,它将数据存储在两个层次。MVL提供了数字数据量的增加在一瞬间通过一根电线进行传输,这可能会显著减少互连的数量。减少的芯片面积和,以及信息容量和计算能力的增加。

现有的基于电荷存储的存储器,如静态随机存取存储器、动态随机存取存储器和闪存,由于以下电量损失而面临性能和可靠性问题10nm技术节点。静态随机存取存储器很快,但它自然界中的挥发性。动态随机存取存储器具有较高的存储容量密度,但它在性质上也是挥发性的。需要刷新每隔几毫秒存储一次,这增加了设备的能量需求。

闪存是非易失性的,但它们的操作速度快,续航能力差。近年来,RRAM由于其增强功能而成为一项非常特殊的技术存储密度、长数据保留期、低功耗、低成本,高速、可扩展性和与现有系统的向后兼容性CMOS技术。

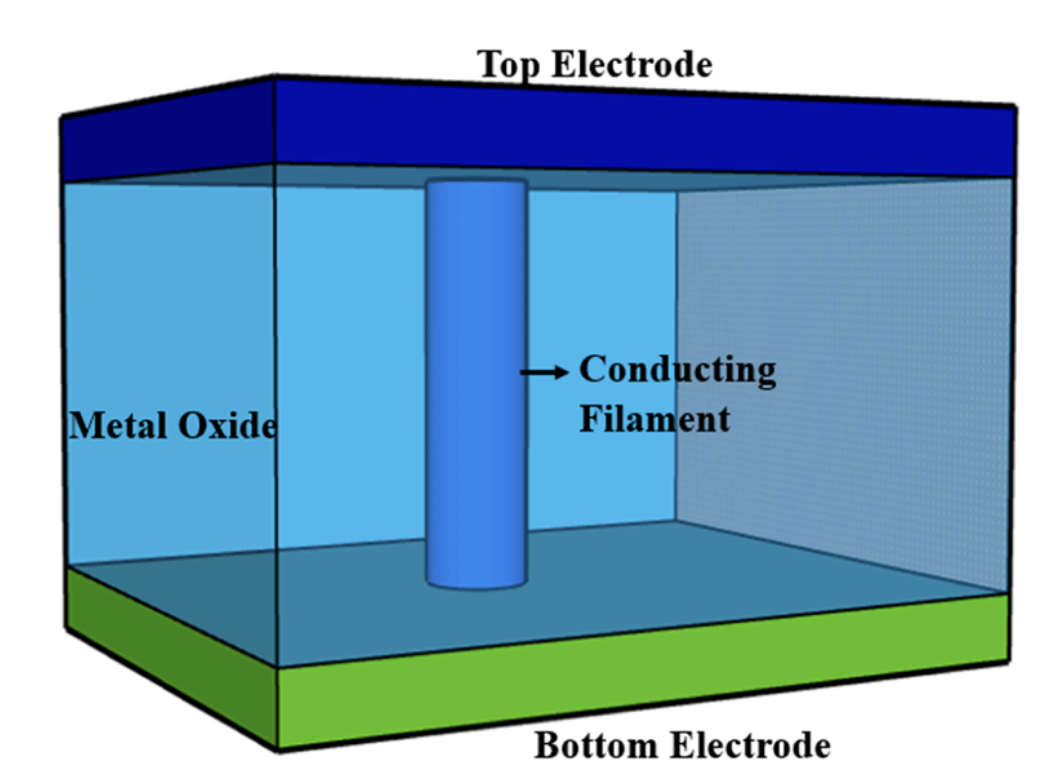

RRAM是一种双端器件,具有绝缘介质位于两个顶部和底部金属电极之间,形成金属绝缘体金属结构,在其端子之间施加电压过程,负责电阻切换的是基于金属的运动离子,然后进行氧化还原反应。顶部电极,形成基于金属离子的RRAM的阳极由Ag、Cu或Ni形成,并且是可氧化的,而底部电极(阴极)成比例地是惰性的。导电细丝的形成发生在顶部电极的溶解,随后是阳离子的移动通常为Ag+或Cu+),最后将其沉积在底部电极上。

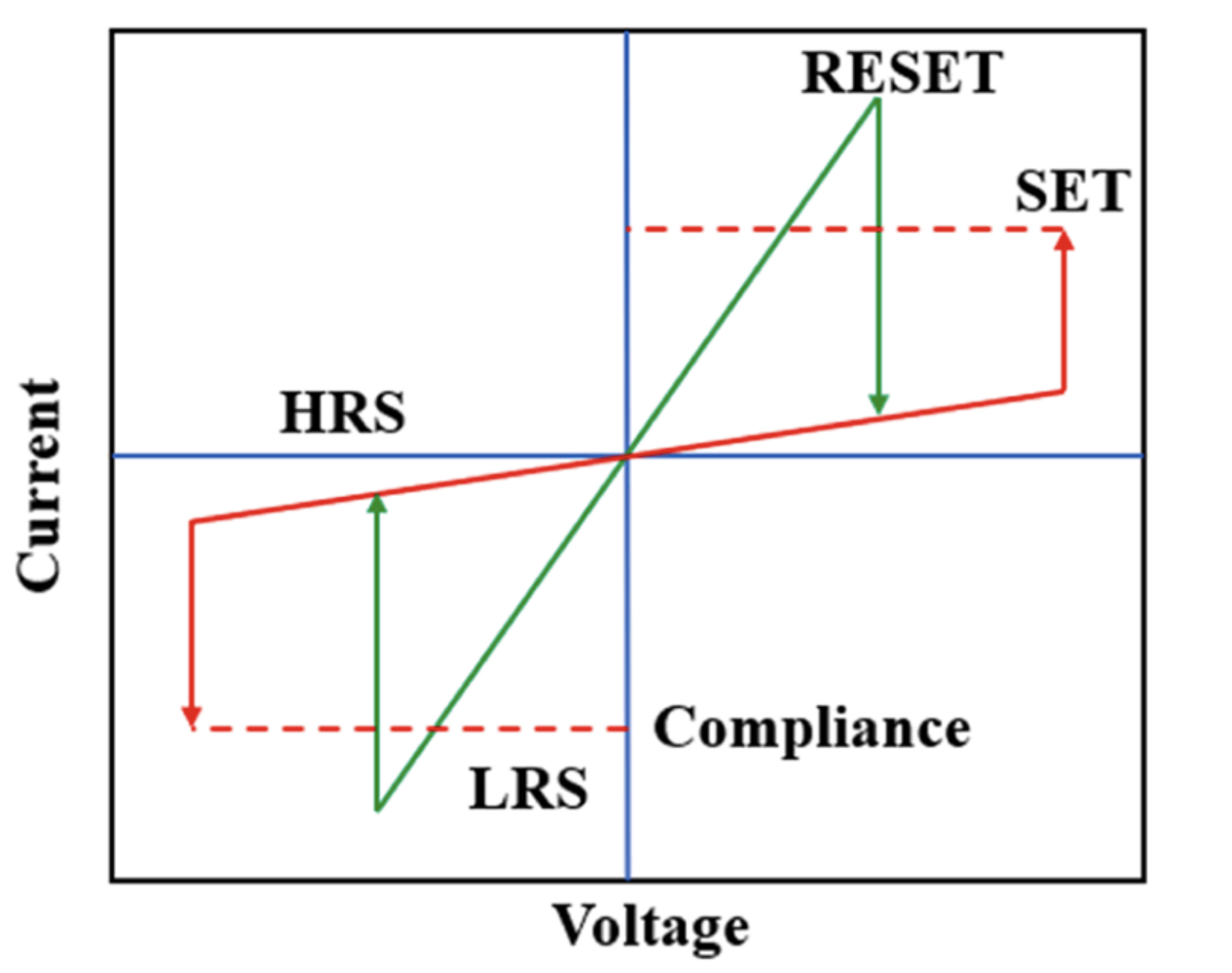

当RRAM从自然HRS切换到LRS时导电丝在一个称为电铸的过程中断裂,在取决于氧化物厚度和电池的形成电压下发生,地区当RRAM从LRS切换到HRS时,会发生RESET过程复位电压(VRESET)。RRAM从HRS到LRS的转换在SET电压(VSET)下的SET过程期间发生。

它遵循线性路径(因为RRAM表现为线性电阻器),直到负电压达到VRSEST。在VRESET阻力突然增加,启动RRAM的过渡进入RESET模式。为了避免在SET和RESET过程,施加一个称为顺应性电流的指标RRAM上的最大电流。RRAM所能承受的最大电流不影响雪崩倍数的称为顺应性电流。

它在SET到RESET和RESET到SET过程中都被强制执行。持久性、数据保留和一致性是RRAM的三个重要性能指标。随着时间的推移,状态之间的连续切换会降低RRAM的性能。耐力量化RRAM可以在这两个状态之前的两个电阻状态不再可区分。

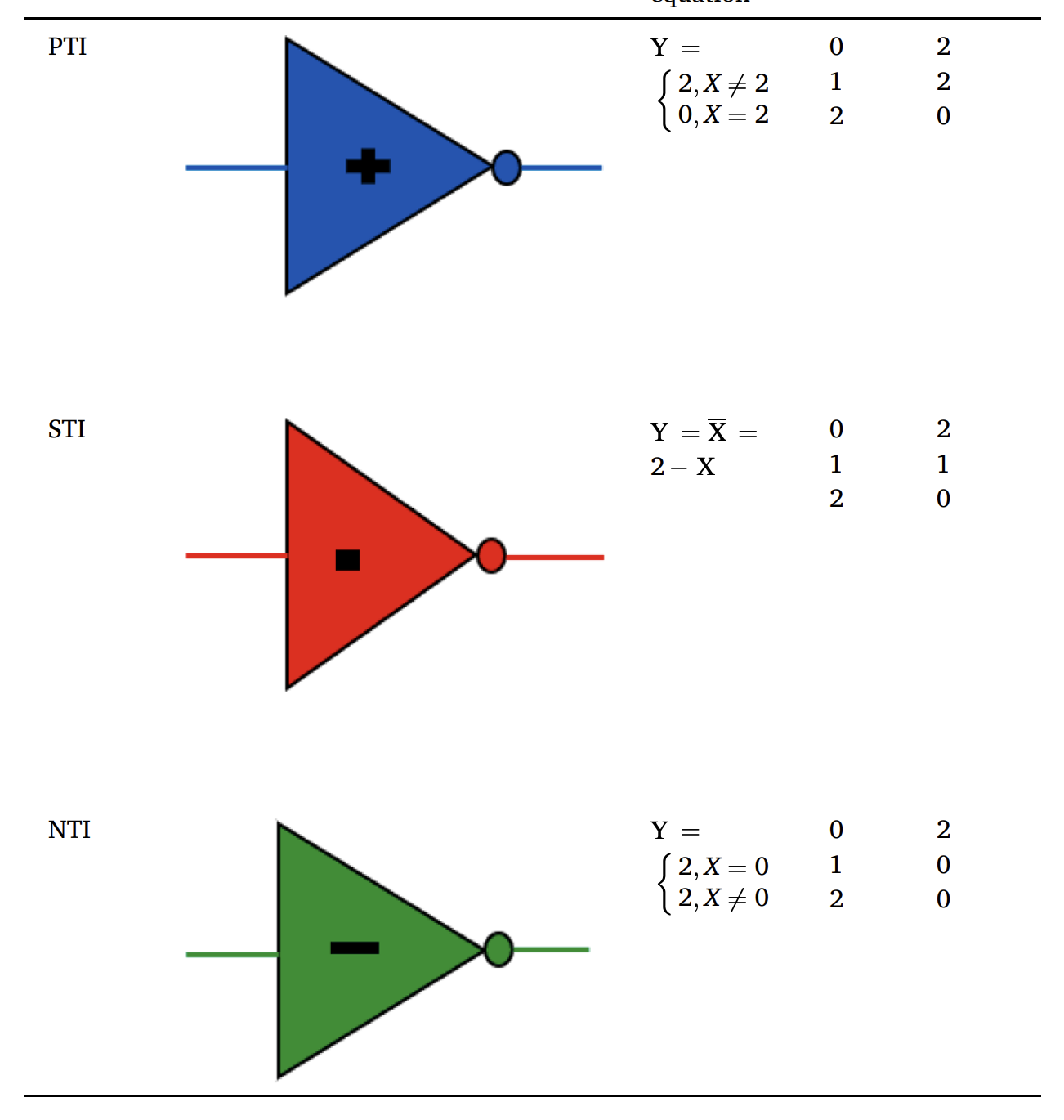

与二进制逻辑相反,三进制逻辑采用三个级别:0、1和2,其由0V、VDD/2和VDD表示。在使用0.9V的电源电压。因此,逻辑0、1和2的值为分别为0V、0.45 V和0.9 V。三元逻辑中的构建块代数是正三元反相器(PTI),标准三元反相器(STI)和负三元反相器(NTI)。这些逆变器的符号、布尔方程和输入输出关系。

RRAM通过在其终端。RRAM充当开关,取代中的CNTFET设计,提供了减少组件数量和面积的优势开销传统的CMOS电阻三值反相器,输入端为-VCC时,T1为ON,T2为OFF;无电流流经电阻器,因此输出为+VCC或逻辑2。什么时候+VCC在输入端T1,T1为OFF,T2为ON,输出端为-VCC或逻辑0。对于输入端的0V或逻辑1,两个晶体管都处于导通状态,并且输出需要进入逻辑1,使用大型电阻值。所提出的基于CNTFET-RRAM的三元逆变器,它避免了使用电阻器并取代了这些电阻器具有RRAM的大型电阻器。

在传统的电阻三值反相器设计中,CMOS晶体管被CNTFET(X1和X5)、电阻器R1和R2取代具有RRMS(X2和X4),并且接地的P-CNTFET(X3)用于与RRAM X2串联以降低功耗。设备X3是栅极端子接地的p沟道CNTFET。当X1导通时,X2的阳极处于VDD,因此X2进入LRS,并且源极端X3的连接到VDD。对于X3,Vgs=Vg−Vs=0−0.9=−0.9V,其小于其Vth(-0.34V)。因此,它导通并提供从输出到VDD的传导路径。当X1关闭时,的阳极X2与正电压断开,因此它进入HRS,并且X3的源极端子达到接地电位。现在对于X3,Vg−Vs=0V,这大于其Vth(-0.34V)。

斯坦福大学RRAM模型模拟了所提出的三元电路,列出的一些重要参所提出的性能指标,如功率、延迟和PDP对电路进行了计算,并与现有设计进行了比较。基于CNTFET RRAM的三元逆变器。所提出的基于CNTFET RRAM的三元逆变器仅使用3NTFET和2个RRAM。上拉网络中的一个CNTFET,另一个并且第三晶体管作为泄漏控制晶体管。所提出的设计显示了最少的PDP,这导致了最少的功耗和延迟。在较低的技术节点,泄漏功率是总功耗的主要贡献者。