4,653

社区成员

发帖

发帖 与我相关

与我相关 我的任务

我的任务 分享

分享存储器一般会消耗大部分的系统功耗,就像我们平时使用操作系统一样,一开机就会占用很多的系统资源,虽然说这个系统功耗的损失,对于许多系统来说可能不是一些关键问题,但是对于物联网(IoT)边缘设备而言,总功耗是非常重要的。几乎所有系统的存储需求都在不停的变化。虽然新的存储器和存储器架构已经筹划了很长时间,但仍未被广泛采用。

在过去相当长的一段时间中,存储器的结构还是以SRAM和DRAM已经成为主力,FLASH结构也是最近几年加入了“战场”,但是在不断的实践和落地的过程中,发现一个问题,所有这些存储结构在往较小的几何结构缩放的过程中都存在问题,部分是因为它们都是平面结构。

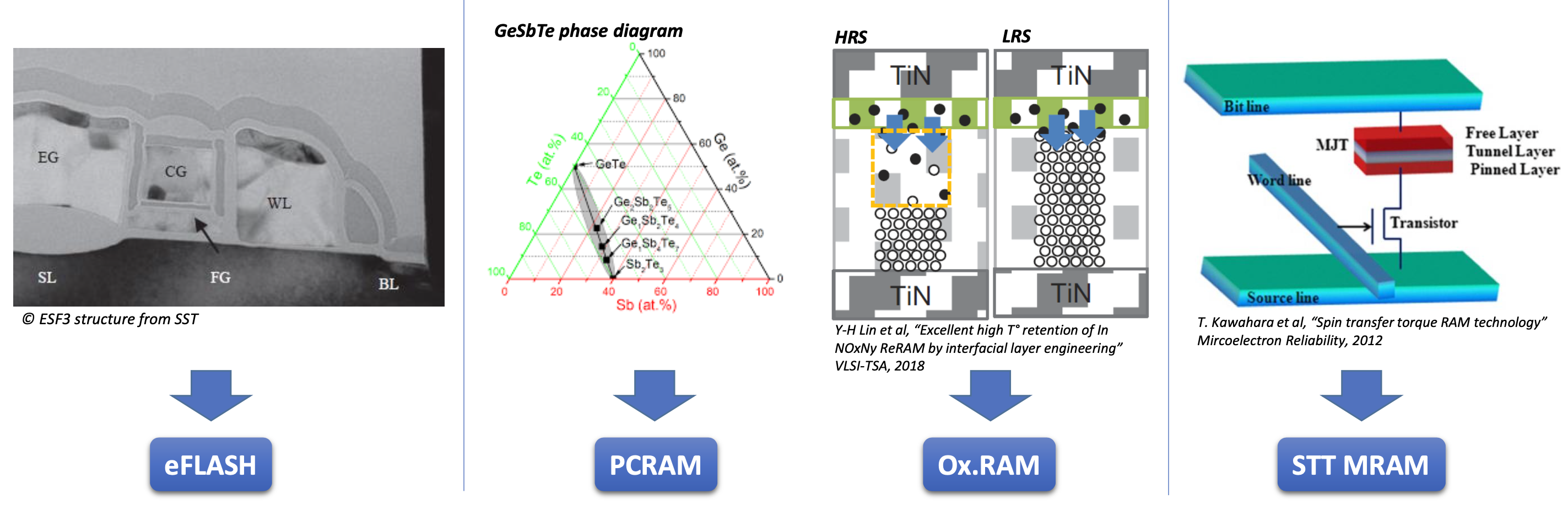

引人注目的新存储器包括:相变存储器(PCM)、铁电存储器(FeRAM)、磁阻RAM(MRAM)、电阻RAM(RRAM或 ReRAM)、自旋转移力矩RAM(STT-RAM)、导电桥RAM(CBRAM)、氧化物电阻存储器(OxRAM),与性能直接相关的是功耗,在给定功耗下的性能是一个非常重要的因素。在不同的应用中,存储器的用途非常不同,而且需求也是变化的,没有一个解决方案可以解决所有问题。

嵌入式存储器技术正是处在于一个“crossroads”十字路口的发展阶段,在从FD-SOI、FinFET先进的CMOS技术中我们可以从中发现,传统的浮栅嵌入式非易失性存储器(eNVM)的集成在28nm和更小的硅几何结构下是一个重大的技术挑战。

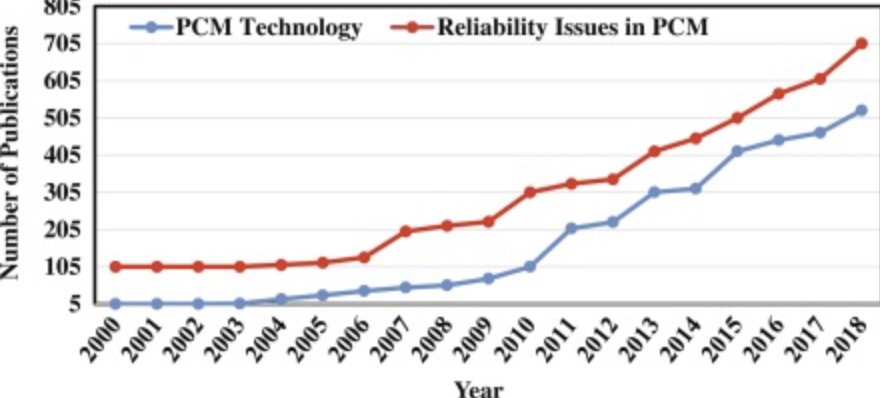

PCM已成为下一代存储器技术的主要竞争者,在基础材料、器件工程和芯片级演示方面取得了令人印象深刻的进展,包括PCM编程和3D堆叠的潜力。此外,通过对这项技术的失效机制有着大量的了解。我们可以在图中,显示了过去十年中在IEEE Xplore、ACM和Google Scholar数据库中发表的关于PCM技术、其适用性和可靠性的文章数量。

PCM在最开始的产品预期开发过程中,旨在取代手机中的NOR闪存,在与NOR相比,PCM产品规格更好,专门用于与LPDDR DRAM集成。可以想像一下,数千万台此类设备用于手机,显示出PCM所能实现的预期功能。这也是可能是当时基于非充电的固态存储器芯片上出货量最大的一次。

然而,随着“智能手机”的出现和低成本、高密度NAND芯片的日益普及,手机架构迅速从基于NOR的“就地执行”架构转变为基于NAND的“存储和下载”架构。在PCM操作中,不希望的“邻近干扰”效应与“热串扰”有关,热串扰是指编程单元产生的热量可以传播到未编程的相邻单元的概率。NOR闪存市场的机会很快就消失了,它不再是PCM可行的途径。

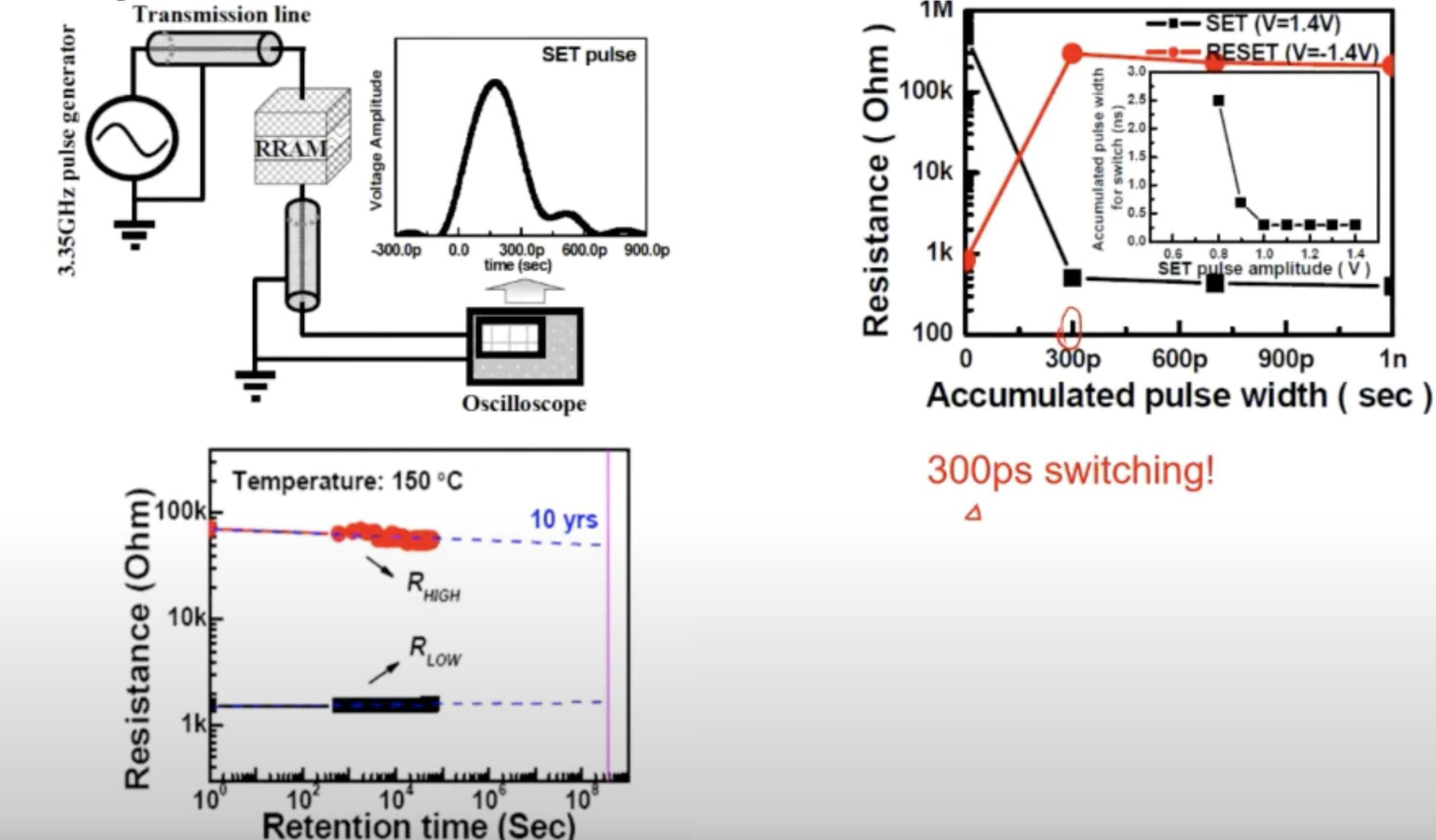

基于PCM的固态驱动器(SSD)也在系统中开发和原型化,PCM与NAND耦合在同一磁盘中。与NAND相比,SSD的性能显著提高,新的NVM技术基于特定外来材料的功能特性,采用了与闪存技术完全不同的物理机制,并为破坏性的28nm CMOS过渡带来的工艺集成困难提供了更有效的解决方案。在这些新的NVM技术中,通常被称为“新兴存储器”,最成熟的是相变存储器(PCM)。

与其他数字系统一样,服务器也享受着摩尔定律的影响。

存储类存储器(SCMs)长期以来一直被认为是一种很有前途的技术,可以弥合主存储器和存储器之间的差距。然而,它们的采用花了很长时间,现在才开始被用作高性能固态硬盘(SSD)。从供应链管理技术的特点和成本两个方面探讨了这种情况的背景和原因。一些供应链管理技术现在开始成熟,有迹象表明供应链管理可能正在扭转局面,实现其最初的承诺。可以通过确定利用SCM特性的引人注目的应用程序来加速这一趋势。大规模服务器应用程序的领域似乎有潜力真正使用SCMs作为传统主存储器的扩展,本文研究了SCMs在这些应用程序中的有效性。

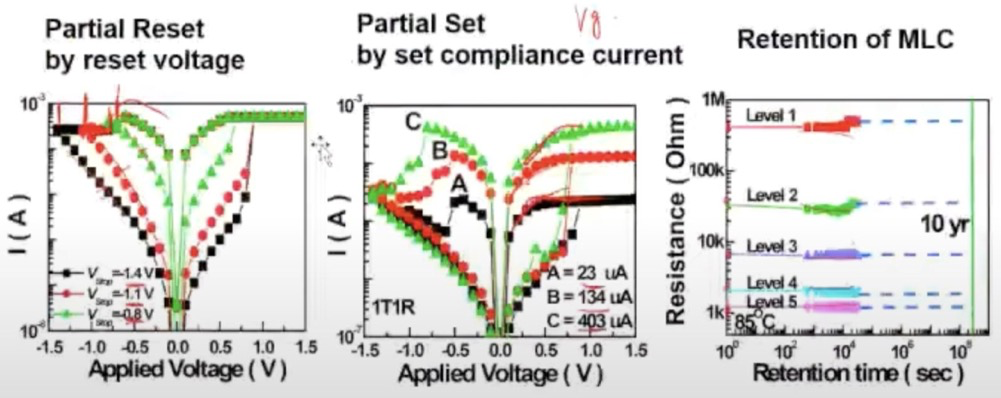

CM阵列类似于采用DRAM技术构造的传统存储器。我们使用稍微修改过的CACTI来精确建模垂直对齐的MLC PCM模型、所提出的访问逻辑和外围访问电路。作为基线,我们使用90 nm 2位MLC PCM原型[9],使用振幅为250μa、持续时间为150 ns的SET脉冲和振幅为150μa、连续时间为40 ns的RESET脉冲。

相变存储器(PCM)利用相变材料中非晶相和结晶相的电阻率之间的大差异的数量级。PCM单元中的相变材料位于两个电极之间,并且施加电流以在两相之间重复地切换材料(或者阻断电流路径的至少一部分材料)。由于所谓加热器上方的开关体积的形状。加热器与相变材料进行小面积接触,流过加热器的电流将加热器正上方的热量集中在相变材料中。在完全集成的晶片上进行PCM制造后,相变材料通常处于结晶状态,因为一些后端生产线制造步骤包括高温工艺,通常加热到400°C达30米

每个存储单元都连接到一个访问设备,该访问设备提供这些电脉冲。熔化相变材料所需的高重置电流是PCM最具挑战性的问题之一。在许多集成晶片单元设计中,存取器件是比实际PCM单元大得多的晶体管。金属氧化物半导体场效应晶体管(MOSFET)和双极结晶体管(BJT)已被描述为单元选择器或存取器件。具有MOSFET作为选择器件的典型存储单元阵列被布置在连接到相变元件的位线和连接到MOSFET的栅极的字线中,并且每个单元可以被单独寻址。如果使用MOSFET或BTJ,存储密度由访问设备的大小决定,而不是由存储单元本身决定。

存储器存储密度可以测量为每个特征的位数的平方,其中特征F是最小的光刻特征尺寸。在交叉点阵列结构中,如果存储单元和存取器件的大小为1F加上相邻单元之间的空间为1F,则可以实现最高可能的存储密度,因此最小可能的占地面积为4F2。这在PCM技术中是非常具有挑战性的。通过使用pn二极管作为接入器件实现了5.8F2的相对较小的占地面积,对于优化的PCM单元设计和材料选择,PCM器件建模非常有吸引力。然而,由于影响PCM器件性能的因素太多,因此它也相当复杂,并且已经应用了各种方法,包括求解分析方程和应用有限元和有限差分技术。

Pool-Frenkel模型也可用于计算在非晶相中观察到的电阻漂移。在该模型中,随着时间的推移,电阻漂移到更高的值对应于由缺陷湮灭和结构弛豫引起的陷阱之间的平均距离Δz的增加。这导致EC的增加,从而也导致电阻、激活能和阈值电压的增加,对于PCM操作阈值的完整建模,还需要了解切换。尽管阈值切换的物理基础的某些方面仍存在争议,该模型可以计算阈值切换过程中的I-V特性,与实验非常一致。该模型基于这样的假设,即在阈值场以上的高场下,电子获得大量能量,使其能够从低能态移动。

随着数量的增加,成本将下降,这将加速它的应用。不久后,许多物联网系统将别无选择,尤其是如果它们想利用新的制造技术节点的话。许多互连架构针对现有存储器类型进行了优化,DDR接口不太适合NVM。使用DDR,首先要声明你想要寻址的行或页面,然后声明你是要读取或写入。