4,664

社区成员

发帖

发帖 与我相关

与我相关 我的任务

我的任务 分享

分享引言:

随着信息技术的飞速发展,计算机系统的性能需求也在不断增长。在现代计算机系统中,动态随机存取存储器(DRAM)扮演着至关重要的角色,作为主要的内存存储器之一,它承担着存储和访问数据的重要任务。然而,随着技术的进步和应用场景的不断拓展,对DRAM产品性能和稳定性的要求也日益提高。

为了满足这些需求,DRAM制造商不断进行技术创新和工艺优化,以提升DRAM产品的性能和可靠性。在这个过程中,马鞍状鳍(也作:鞍鳍工艺Through Saddle Fin)作为一种关键的结构工艺,引起了广泛关注。马鞍状鳍的优化不仅可以改善DRAM器件的性能,还可以提高其稳定性和可靠性,从而满足日益增长的计算需求。

本文旨在深入探究DRAM产品的结构及马鞍状鳍的作用。首先,我们将介绍DRAM产品的基本结构,包括存储单元、字线、位线等关键组件,并解释它们在DRAM中的作用和相互关系。然后,我们将重点讨论马鞍状鳍的概念和作用,包括马鞍状鳍的形成过程、结构特点以及对DRAM性能的影响。通过对马鞍状鳍工艺的深入理解,我们可以更好地认识其在DRAM中的作用,为进一步的优化和改进提供理论支持。

在本文的后续部分,我们将详细探讨马鞍状鳍工艺的优化对DRAM产品性能的影响,以及其在当前DRAM市场中的地位和未来发展趋势。最后,我们将总结本文的主要内容,并展望马鞍状鳍工艺在未来DRAM技术发展中的潜在应用和重要意义。

通过本文的阐述,我们旨在为读者提供对DRAM产品结构及马鞍状鳍的全面理解,帮助读者更好地了解和应用这一重要技术,在不断变化的信息时代中保持竞争优势。

在现代计算机系统中,动态随机存取存储器(DRAM)是一种关键的组件,用于存储数据和指令。了解DRAM产品的结构和其关键组成部分,如马鞍状鳍,对于理解其工作原理和性能至关重要。本文将深入探讨DRAM产品的结构、马鞍状鳍的作用,以及不同结构对DRAM产品性能的影响。

DRAM产品通常由多个存储单元组成,每个存储单元都包含一个存储器电容器和一个访问晶体管。这些存储单元被组织成行和列,以便对其进行地址编址和访问。DRAM的基本结构包括以下几个主要组件:

存储单元(Cell): 每个存储单元由一个存储器电容器和一个访问晶体管组成。电容器存储一个位(0或1),而晶体管用于控制对电容器的访问。

字线(Word Line): 字线是用于选择存储单元的行。当字线被激活时,与之相连的所有存储单元都被激活,可以读取或写入数据。

位线(Bit Line): 位线是用于读取或写入数据的列。通过激活适当的字线和位线,可以选择特定的存储单元进行数据访问。

控制线: 控制线用于控制DRAM的各种操作,如读取、写入、刷新等。它们包括预充电线、行选通线等。

马鞍状鳍是一种用于增加DRAM性能和稳定性的重要结构。它是在DRAM存储单元之间形成的一种鳍状结构,具有一定的高度和曲率。马鞍状鳍通常由硅材料构成,其形成需要特定的加工步骤。马鞍状鳍的主要作用包括:

增加通道长度: 由于马鞍状鳍位于存储单元之间,它们增加了访问晶体管的通道长度。这有助于减少短通道效应,提高晶体管的性能和可靠性。

增加数据保留时间: 马鞍状鳍可以提供更大的表面积,从而增加存储电容器的电荷存储能力。这可以延长数据在DRAM中的保持时间,从而减少刷新频率并提高功耗效率。

改善读写性能: 通过优化马鞍状鳍的结构和形状,可以改善DRAM的读写性能,包括读取延迟、写入速度和数据保持稳定性。

不同的马鞍状鳍结构和加工参数会对DRAM产品的性能产生重要影响。以下是一些常见的结构和其对性能的影响:

鳍高度: 较高的马鞍状鳍可以提供更长的通道长度和更大的存储电容器表面积,从而改善性能和稳定性。

鳍曲率: 适当的鳍曲率可以减少短通道效应并提高晶体管的控制能力,但过大的曲率可能导致制造困难和性能损失。

鳍间距: 适当的鳍间距可以平衡通道长度和集成度,从而实现性能和面积的最佳组合。

加工精度: 更精细的加工工艺可以产生更一致和稳定的马鞍状鳍结构,从而提高DRAM产品的性能和可靠性。

随着DRAM技术节点的不断缩小,访问晶体管问题因栅极控制能力不足而备受关注。为了增加通道长度、防止短通道效应以及提高数据保留时间,人们随后引入了具有埋藏通道阵列晶体管(BCAT)的马鞍状鳍结构。然而,在20纳米技术节点之后,确保足够的器件性能(如保持时间和驱动控制能力)变得更加具有挑战性。因此,DRAM制造商一直在寻找方法,在不改变现有DRAM器件方案的情况下,通过使用BCAT来改善器件性能。为了提高DRAM马鞍状鳍的性能,可以利用虚拟工艺建模来研究鳍结构的影响并开发最佳的鳍结构。

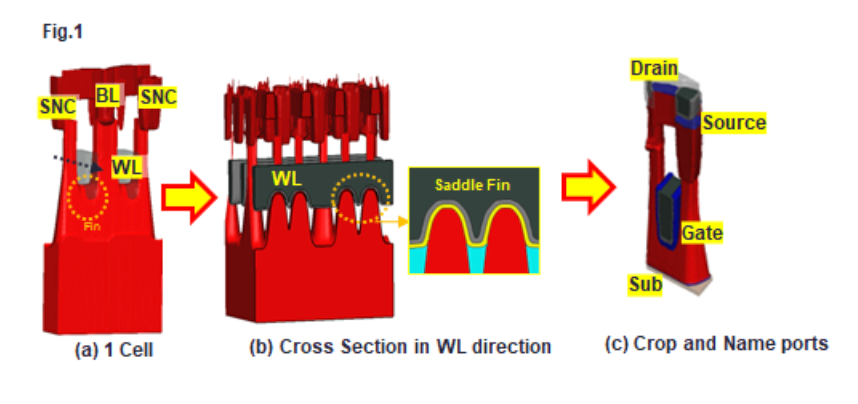

在传统DRAM中,单个存储单元包括2个字线(WLs)、一个位线(BL)和2个存储节点接触(SNC),如图1(a)所示。马鞍状鳍是在字线刻蚀步骤(在字线金属沉积之前)中形成的,位于单元字线下方,如图1(b)中黄色虚线圆圈所示。通过在字线方向上进行垂直切割(图1(b)),可以详细观察马鞍状鳍的结构。在器件模拟过程中,可以通过在SNC工艺后虚拟裁剪晶体管,并在栅极、源极和漏极处添加端口来测量马鞍状鳍的性能,如图1(c)所示。

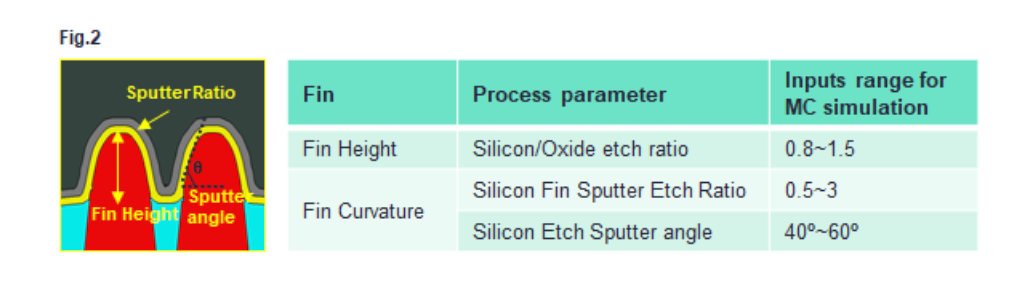

可以关注影响鳍结构和器件性能的重要工艺参数。在相关的研究中,可以假设在马鞍状鳍设计方案中,活动区域(AA)和字线CD应该保持不变,因此可以只优化鳍结构本身,包括鳍的高度和曲率。

如图2所示,鳍的高度主要受硅/氧化物刻蚀比的影响。而鳍的曲率受到硅鳍溅射刻蚀比以及字线刻蚀步骤中的溅射刻蚀角度的影响。在执行均匀的蒙特卡洛模拟之前,需要设置每个输入参数的范围,并对器件性能进行线性回归。利用SEMulator3D Analytics模块可以找到每个计量目标的重要输入参数,并使用这些重要输入参数为每个选择的目标构建回归模型。

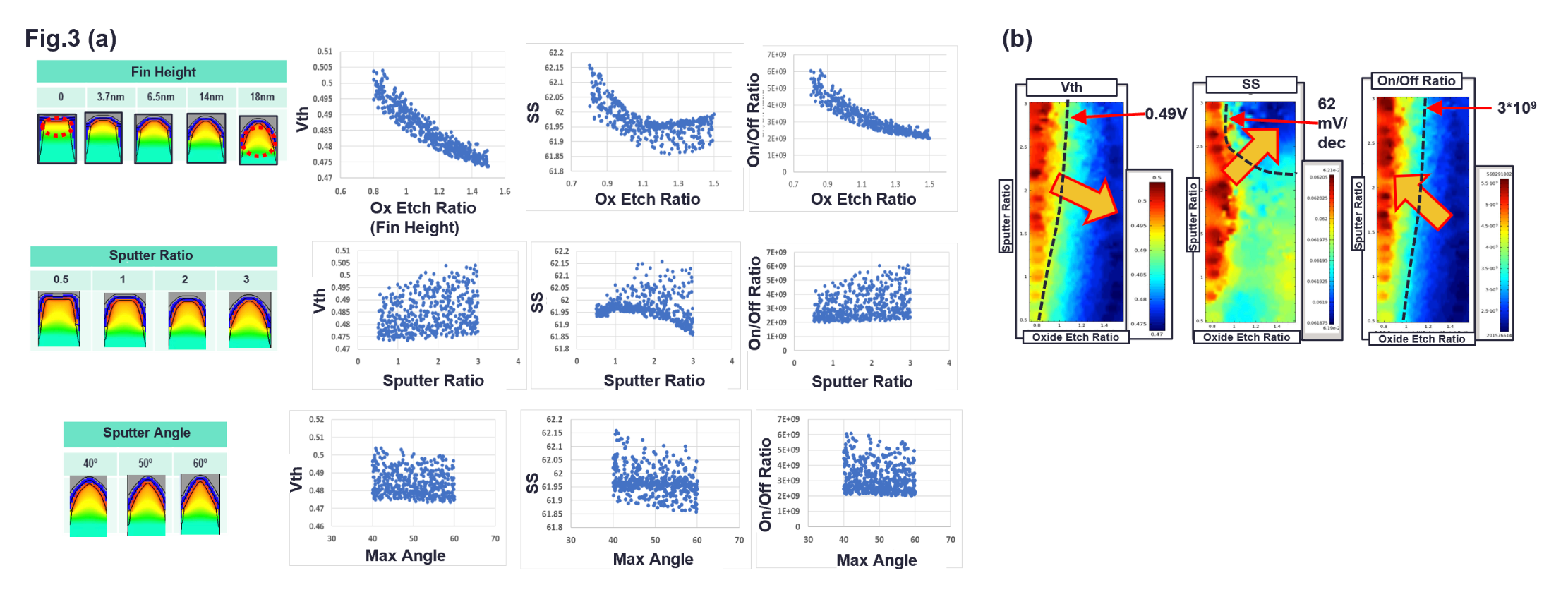

在回归分析后,我们可以通过敏感性分析确定具有统计显著性的工艺参数。一旦确定了这些显著影响性能的工艺参数,就可以简单地通过观察工艺参数与计量目标之间的模拟关系来优化预选的工艺窗口中的各种参数设置。典型结果示例如图3(a)所示。例如,在我们的鳍高度设计实验中,随着鳍高度的增加,Vth会减小,但同时关断电流(Ioff)增加导致开关比也减小。这意味着在优化鳍高度时,需要考虑Vth和开关比之间的权衡。图3(b)显示了等高线图,可同时查看两个工艺参数与任选计量目标之间的关系。通过敏感性分析和线性回归功能,我们可以确定最佳的工艺参数范围。例如,如果我们希望Vth小于0.49V,SS小于62mV/dec,Ion/Ioff大于3×10^9,则最佳的工艺条件是氧化物刻蚀比在1.0至1.2之间,溅射比大于2,并且最大刻蚀角度大于50度。

这些类型的研究可用于确定产生最佳器件性能的最佳鳍高度和鳍曲率。这些研究结果可以用来开发当前或下一代DRAM产品的高性能马鞍状鳍结构配置。

优化马鞍状鳍工艺可以显著改善DRAM器件的性能和稳定性,DRAM制造商可以生产出性能更优、功耗更低的产品,从而在市场上获得更大的竞争优势。高性能的DRAM产品能够满足客户对于数据处理速度和性能稳定性的需求,进而提升品牌知名度和市场份额。

与此同时,马鞍状鳍工艺的优化不仅可以改善现有产品的性能,还可以推动DRAM技术的进一步发展。通过不断优化工艺和结构,可以实现DRAM产品在性能、功耗、可靠性等方面的全面提升,引领整个存储器技术的发展方向。

尽管马鞍状鳍工艺的优化为DRAM市场带来了巨大的机遇,但市场也面临着一些挑战:

技术难度:马鞍状鳍工艺的优化需要高度精密的制造工艺和设备支持,技术难度较大,需要克服各种制造难题。

成本压力:在追求性能提升的同时,DRAM制造商还需要保持产品的成本竞争力。优化工艺可能会带来额外的制造成本,需要平衡性能提升与成本控制之间的关系。

竞争激烈:DRAM市场竞争激烈,国内外众多厂商竞争激烈,制约着产品价格和利润空间。

通过马鞍状鳍工艺的优化,可以有效提升DRAM器件的性能。马鞍状鳍作为一种重要的结构,在DRAM中起着关键的作用。它能够增加通道长度,防止短通道效应的发生,提高数据保留时间,从而减少刷新频率并提高功耗效率。通过调整马鞍状鳍的结构参数,如鳍高度、鳍曲率等,可以进一步改善DRAM的读写性能、稳定性和功耗表现。随着技术的进步和工艺的改进,马鞍状鳍将继续发挥着重要的作用,推动DRAM器件向着更高性能、更低功耗的方向发展。因此,对马鞍状鳍工艺的深入研究和优化对于提升DRAM器件性能具有重要意义。

参考文献:

正文字数:3269

支持存内计算开发者社区

支持存内计算开发者社区

支持存内计算开发者社区

支持存内计算开发者社区

优化马鞍状鳍工艺可以显著改善DRAM器件的性能和稳定性~

存内计算支持的算子较少,设计灵活度不如近数据计算的逻辑层

存内计算支持的算子较少,设计灵活度不如近数据计算的逻辑层